GPIO(英语:General-purpose input/output),通用型之输入输出的简称,功能类似8051的P0—P3,其接脚可以供使用者由程控自由使用,PIN脚依现实考量可作为通用输入(GPI)或通用输出(GPO)或通用输入与输出(GPIO),如:clk generator, chip select等。

既然一个引脚可以用于输入、输出或其他特殊功能,那么一定有寄存器用来选择这些功能。对于输入,一定可以通过读取某个寄存器来确定引脚电位的高低;对于输出,一定可以通过写入某个寄存器来让这个引脚输出高电位或者低电位;对于其他特殊功能,则有另外的寄存器来控制它们。

GPIO(General Purpose Input/Output,通用输入/输出)是一种灵活的接口,用于与各种外部设备进行通信。它广泛应用于微控制器、单板计算机(如Raspberry Pi)和嵌入式系统中。以下是GPIO工作原理的详细解释:

1. 引脚配置GPIO引脚可以配置为输入或输出模式。不同模式下,GPIO引脚的行为不同:

输入模式(Input Mode): GPIO引脚用于接收外部信号,例如读取按钮状态或传感器数据。

输出模式(Output Mode): GPIO引脚用于发送信号控制外部设备,例如点亮LED或驱动马达。

2. 电平状态GPIO引脚可以设置或读取两种电平状态:

高电平(High Level): 一般对应于逻辑1,电压通常是设备的工作电压(如3.3V或5V)。

低电平(Low Level): 一般对应于逻辑0,电压接近于0V。

3. 输入引脚输入引脚可以检测外部电平状态,并将该状态传递给微控制器。常见的操作包括:

读取引脚状态: 通过代码读取引脚的电平状态(高或低)。

上拉/下拉电阻: 为了确保引脚在未连接外部设备时有确定的电平状态,可以启用内部上拉或下拉电阻。上拉电阻将引脚电压拉高到高电平,下拉电阻则将引脚电压拉低到低电平。

4. 输出引脚输出引脚用于驱动外部设备。常见的操作包括:

设置引脚状态: 通过代码将引脚电平设置为高或低,从而控制外部设备的工作状态。

PWM(脉宽调制): 通过快速切换引脚的高低电平,生成模拟信号,用于控制设备的亮度、速度等。

5. 中断(Interrupts)一些GPIO引脚支持中断功能。当引脚状态发生变化时,可以触发中断,通知微控制器进行特定的处理。这在需要快速响应的应用场景中非常有用,例如按钮按下的瞬间检测。

二、STM32引脚分布图

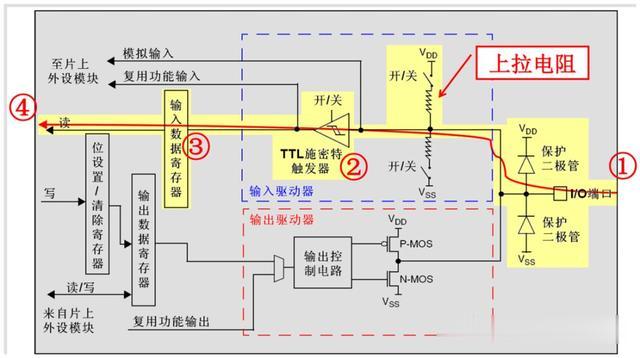

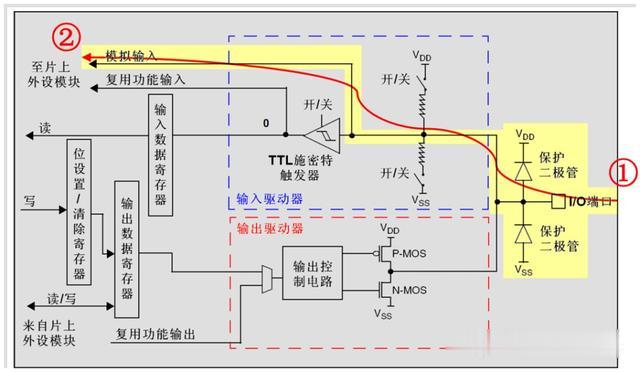

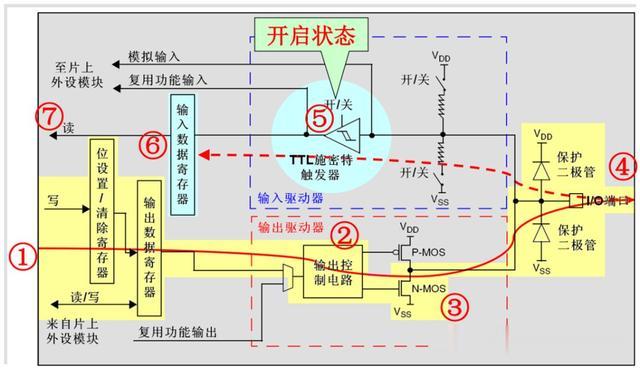

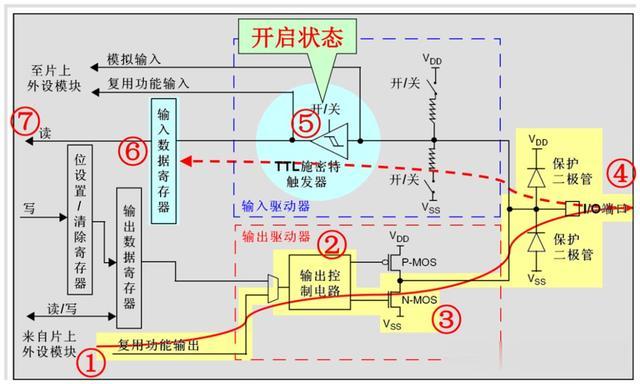

每个GPIO内部都有这样的一个电路结构,这个结构在本文下面会具体介绍。

保护二极管:

IO引脚上下两边两个二极管用于防止引脚外部过高、过低的电压输入。当引脚电压高于VDD时,上方的二极管导通;当引脚电压低于VSS时,下方的二极管导通,防止不正常电压引入芯片导致芯片烧毁。但是尽管如此,还是不能直接外接大功率器件,须加大功率及隔离电路驱动,防止烧坏芯片或者外接器件无法正常工作。

这个二极管,也会导致IO接口不支持热插拔。

热插拔技术详解(上)

热插拔技术详解(下)

P-MOS管和N-MOS管:

由P-MOS管和N-MOS管组成的单元电路使得GPIO具有“推挽输出”和“开漏输出”的模式。这里的电路会在下面很详细地分析到。

TTL肖特基触发器:

信号经过触发器后,模拟信号转化为0和1的数字信号。但是,当GPIO引脚作为ADC采集电压的输入通道时,用其“模拟输入”功能,此时信号不再经过触发器进行TTL电平转换。ADC外设要采集到的原始的模拟信号。

这里需要注意的是,在查看《STM32中文参考手册V10》中的GPIO的表格时,会看到有“FT”一列,这代表着这个GPIO兼容3.3V和5V的;如果没有标注“FT”,就代表着不兼容5V。

STM32的GPIO工作方式

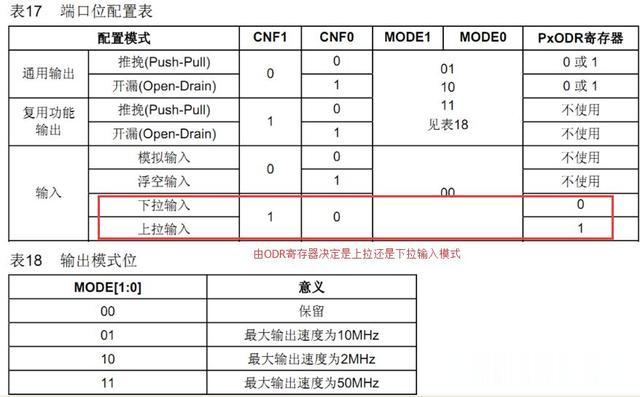

GPIO支持4种输入模式(浮空输入、上拉输入、下拉输入、模拟输入)和4种输出模式(开漏输出、开漏复用输出、推挽输出、推挽复用输出)。同时,GPIO还支持三种最大翻转速度(2MHz、10MHz、50MHz)。

每个I/O口可以自由编程,但I/O口寄存器必须按32位字访问。

GPIO_Mode_AIN 模拟输入

GPIO_Mode_IN_FLOATING 浮空输入

GPIO_Mode_IPD 下拉输入

GPIO_Mode_IPU 上拉输入

GPIO_Mode_Out_OD 开漏输出

GPIO_Mode_Out_PP 推挽输出

GPIO_Mode_AF_OD 复用开漏输出

GPIO_Mode_AF_PP 复用推挽输出

通常,GPIO配置涉及多个寄存器,每个寄存器都有特定的用途。常见的GPIO寄存器包括:

方向寄存器(Direction Register):配置引脚为输入或输出。

数据寄存器(Data Register):设置或读取引脚的电平状态。

中断使能寄存器(Interrupt Enable Register):启用或禁用中断功能。

中断状态寄存器(Interrupt Status Register):指示中断发生的状态。

上拉/下拉电阻配置寄存器(Pull-up/Pull-down Register):配置上拉或下拉电阻。

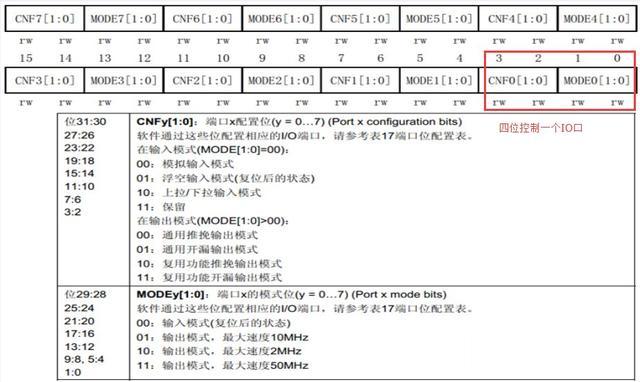

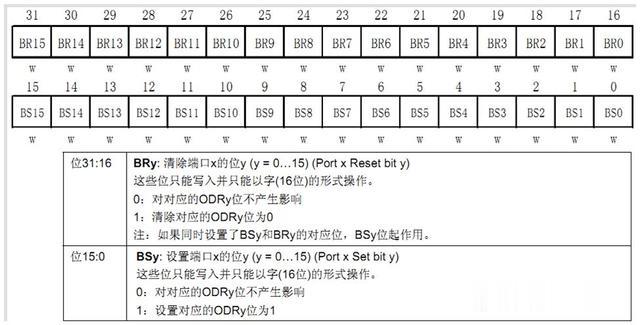

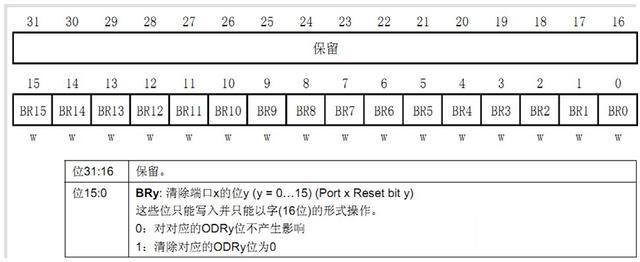

STM32每组GPIO包含系列7个寄存器(7组GPIO共包含7*7=49个寄存器) 两个32位配置寄存器 GPIOx_CRL 低16位 GPIOx_CRH 高16位 两个32位数据寄存器 GPIOx_IDR 输入数据寄存器 GPIOx_ODR 输出数据寄存器 一个32位置位/复位寄存器 GPIOx_BSRR 一个16位复位寄存器 GPIOx_BRR 一个32位锁定寄存器 GPIOx_LCKR 1,端口配置寄存器: STM32每组GPIO位16个IO口,每4位控制一个IO口,所以32位控制8个IO口 分为低16位:GPIOx_CRL和高16位:GPIOx_CRH共32位控制一组GPIO的16个IO口

以GPIOA_CRL为例,配置IO口PA0 -> MODE0=00(输入模式) CNF0=10(上拉/下拉输入模式) 此种配置下到底是上拉还是下拉输入模式还需由ODR寄存器决定

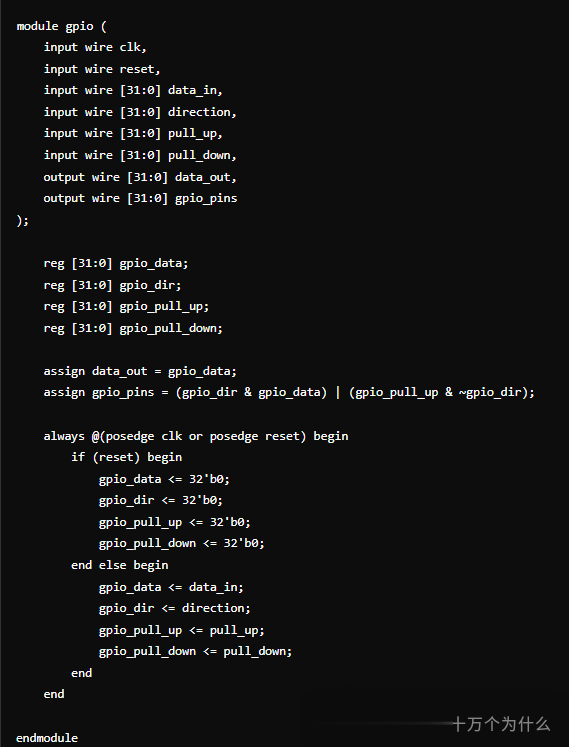

在芯片设计阶段,GPIO模块通过设计特定的硬件逻辑和寄存器集合来实现。芯片工程师会使用硬件描述语言(HDL)如VHDL或Verilog来描述这些功能。下面是一些关键点:

芯片的内部设计

GPIO模块通常包括以下部分:

方向控制逻辑: 决定每个引脚是输入还是输出。

数据寄存器: 存储引脚的电平状态。

中断控制逻辑: 处理GPIO中断请求。

上拉/下拉电阻控制: 管理上拉和下拉电阻的启用与禁用。

寄存器映射硬件设计中,寄存器映射到芯片的特定地址空间。这些地址通过总线系统与CPU相连,CPU可以通过总线系统访问这些寄存器。例如,方向寄存器、数据寄存器、中断使能寄存器等,分别分配到特定的地址。

输入输出端口

clk:时钟信号。

reset:复位信号。

data_in:输入数据,控制GPIO引脚的高低电平。

direction:引脚方向控制,1为输出,0为输入。

pull_up:上拉电阻控制,1启用上拉电阻。

pull_down:下拉电阻控制,1启用下拉电阻。

data_out:输出数据,表示当前GPIO引脚的状态。

gpio_pins:GPIO引脚的实际输出。

寄存器

gpio_data:存储当前GPIO引脚的电平状态。

gpio_dir:存储每个引脚的方向配置。

gpio_pull_up:存储每个引脚的上拉电阻配置。

gpio_pull_down:存储每个引脚的下拉电阻配置。

逻辑

使用assign语句将data_out和gpio_pins连接到相应的寄存器。

gpio_pins的输出取决于引脚方向、数据、上拉电阻和下拉电阻的配置。

always块在时钟上升沿或复位信号有效时更新寄存器的值。

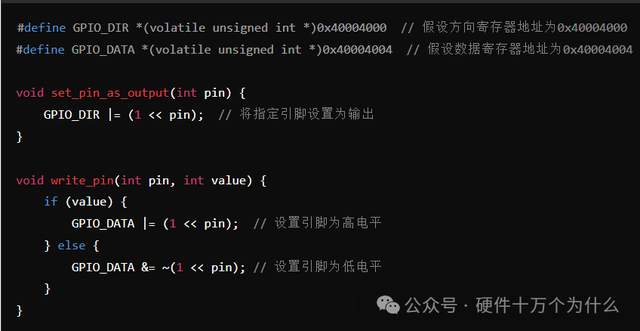

软件控制软件通过访问这些寄存器来控制GPIO。通常使用内存映射I/O(Memory-Mapped I/O)的方法,将硬件寄存器映射到CPU的地址空间,使得CPU可以像访问内存一样访问这些寄存器。

内存映射I/O内存映射I/O通过将寄存器地址映射到处理器的地址空间,使得寄存器可以通过普通的读写操作来访问。下面是一个例子:

在系统初始化时,硬件抽象层(HAL)或驱动程序会设置正确的寄存器地址,并确保这些地址是可访问的。例如,在嵌入式操作系统中,寄存器地址通常定义在头文件中,并在程序中直接使用。

控制逻辑

软件通过操作这些寄存器来实现对GPIO的控制。例如:

配置引脚方向: 写入方向寄存器来设置引脚为输入或输出。

设置引脚电平: 写入数据寄存器来改变引脚的电平状态。

读取引脚状态: 读取数据寄存器来获取引脚的当前电平状态。

启用中断: 写入中断使能寄存器来启用或禁用GPIO中断。

1,端口的复用: 大部分IO口可复用为外部功能引脚,参考芯片数据手册(IO口复用和重映射)

GPIO在芯片设计中通过硬件逻辑和寄存器结合,软件通过内存映射I/O访问这些寄存器,实现对GPIO引脚的配置和控制。理解硬件寄存器和内存映射的基本原理是实现GPIO控制的关键。

参考文档:

《CSDN博客》 BraveWangDev

《GPIO口工作原理的超详细解释》孤芳剑影