JK触发器,作为数字逻辑电路中的一种基础且至关重要的元件,扮演着信息存储和状态转换的关键角色。

在电子工程领域,无论是设计复杂的计算机系统,还是构建简单的计数器或序列发生器,JK触发器都以其独特的功能和高度的灵活性被广泛应用。

本文旨在深入探讨JK触发器的工作原理、设计要点以及在实际中的应用,为读者提供全面的理解和应用指导。

来了解什么是JK触发器。

JK触发器是一种双稳态存储元件,能够根据输入信号的变化存储一个二进制位(0或1),并按照时钟信号的边沿进行状态的更新。

它之所以得名“JK”,是源自于其两个主要输入端——J端和K端,这两个输入端的不同组合决定了触发器的输出状态。

此外,JK触发器还包括一个时钟输入端(CLK)、一个输出端(Q)和一个反相输出端(~Q)。

JK触发器的核心特性在于其对输入信号的高度灵活性处理能力。

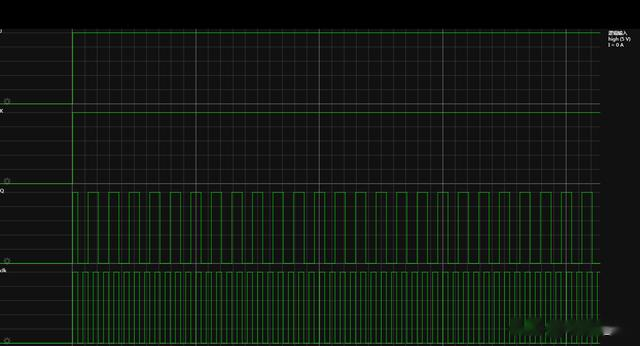

当J端和K端同时为低电平时,无论前一状态如何,触发器都将保持当前状态不变;当J端为高电平而K端为低电平时,触发器将在下一个时钟脉冲到来时将输出置为高电平;反之,如果J端为低电平而K端为高电平,则输出将被置为低电平;最特别的情况是当J端和K端同时为高电平时,触发器的状态会发生翻转,即从高变低或从低变高。

这种灵活的状态控制使得JK触发器能够实现复位、置位、保持和翻转等操作,大大增强了其在逻辑电路设计中的应用范围。

在实际应用中,JK触发器不仅可以单独使用,还可以与其他类型的触发器如D触发器和T触发器相结合,通过适当的电路设计实现更为复杂的逻辑功能。

例如,通过特定的逻辑门配置,可以将JK触发器转换为D触发器或T触发器,从而适应不同的设计需求。

接下来讨论JK触发器的设计原理。

设计JK触发器需要考虑多个方面,包括选择合适的逻辑门、确定时钟信号的频率以及确保输入信号的稳定性等。

在Multisim等数字电路设计和仿真软件中,设计师可以通过拖放组件和连接导线的方式快速搭建JK触发器的电路模型,并通过模拟时钟信号观察其工作状态的变化。

此外,设计者还需要关注触发器的性能指标,如响应时间、稳定性和抗干扰能力等,以确保设计的电路能够满足实际应用的需求。

JK触发器的高级应用涉及变体设计、多级级联及实际电路中的应用案例。

例如,在需要实现多位数同步操作的场景中,可以通过将多个JK触发器级联起来形成移位寄存器或计数器。

此外,JK触发器还广泛应用于数据缓存、信号处理和系统控制等多个电子系统中,展现了其在现代电子设计中的不可替代性。

JK触发器作为一种功能强大的数字逻辑电路元件,不仅在理论上具有重要的研究价值,而且在实际应用中也展现出了极高的灵活性和广泛的应用前景。

无论是对于电子工程师、学生还是爱好者来说,深入了解和掌握JK触发器的工作原理和应用技巧,都是提高电子设计与创新能力的关键一步。