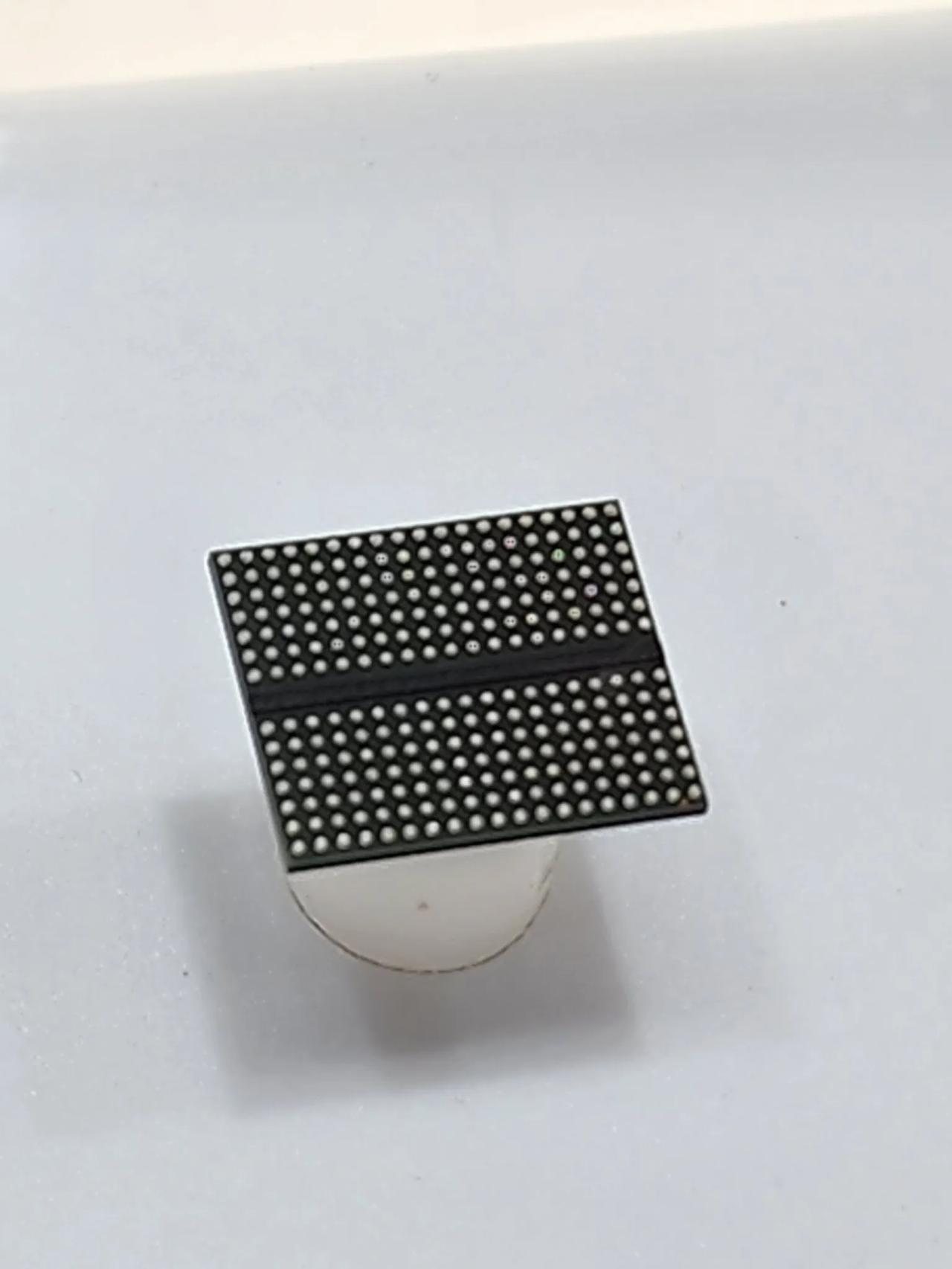

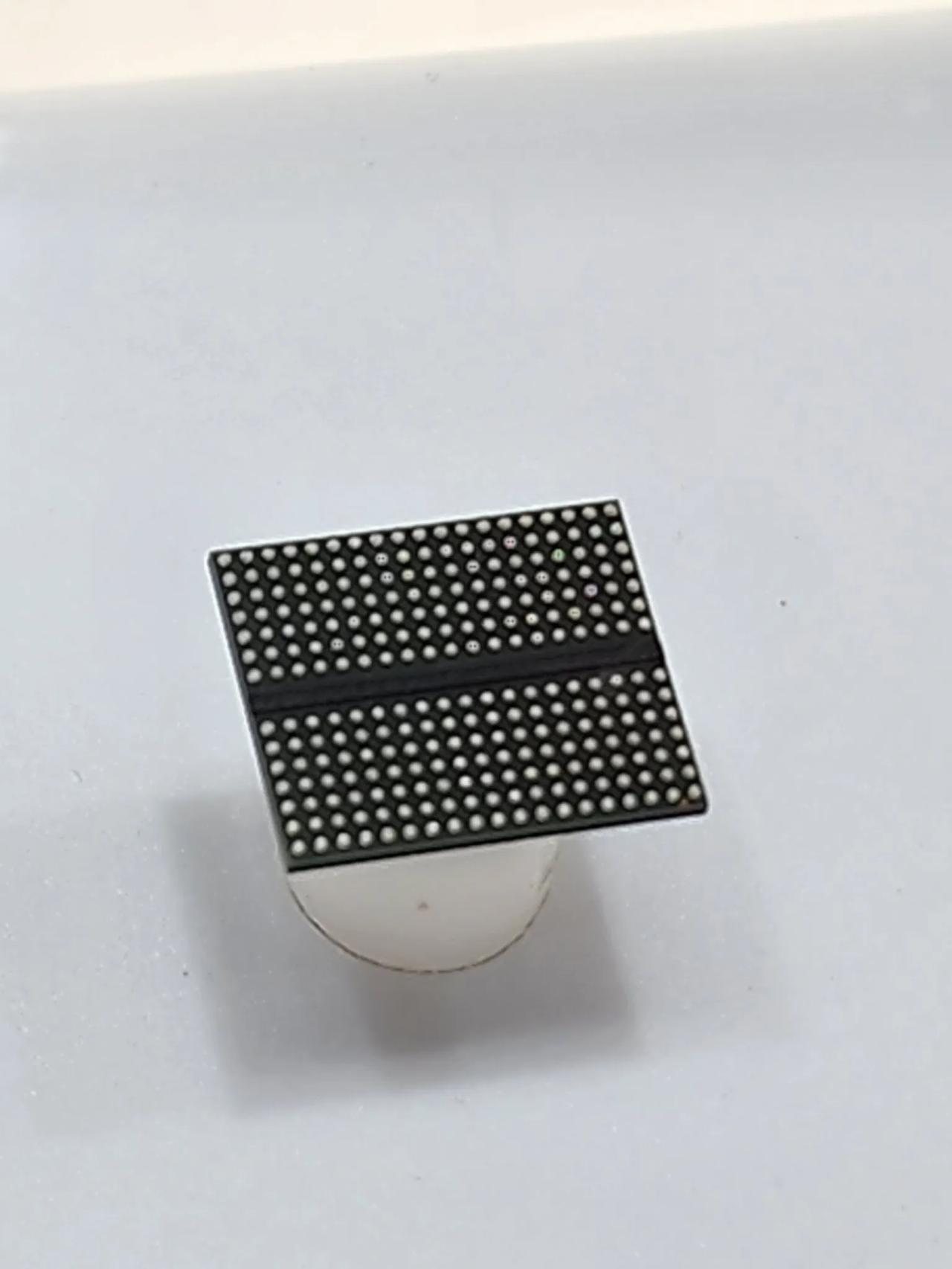

14nm之后,再说什么几nm,往往都是数字游戏了,用晶体管密度来测定更合理 既然如此有人说麒麟9100预计晶体管数量在140亿左右,再看看台积电5nm能做到170亿,所以有人说麒麟9100相当于5.5nm倒也说得过去,但同时也要知道5.5nm和5nm这个坎没有那么容易过去。 所以就目前的情况来看,传闻中的麒麟9100工艺密度应该快到国内的极限了,这的确非常厉害,但后续怎么办也是个问题,最近老美那边疯了,准备下狠手,要卡得更紧了

14nm之后,再说什么几nm,往往都是数字游戏了,用晶体管密度来测定更合理 既然如此有人说麒麟9100预计晶体管数量在140亿左右,再看看台积电5nm能做到170亿,所以有人说麒麟9100相当于5.5nm倒也说得过去,但同时也要知道5.5nm和5nm这个坎没有那么容易过去。 所以就目前的情况来看,传闻中的麒麟9100工艺密度应该快到国内的极限了,这的确非常厉害,但后续怎么办也是个问题,最近老美那边疯了,准备下狠手,要卡得更紧了

评论列表