一、为什么需要“绕等长”

传输线等长包括差分对内等长,也包括相同类型的传输线组内等长。如果传输线不等长会带来一些信号完整性的问题,包括时序不满足要求、损耗过大或者容易受干扰等等。最简单的方式就通过绕线使差分对不同的两段传输线长度一致。

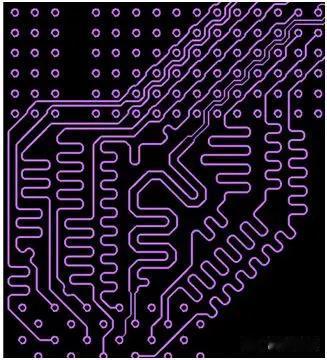

随着高速电路的发展,电路的设计在朝着高速高密度的方向发展。速度和密度高了的话,各种信号完整性、EMI的问题就出来。这也就出现了各种各样的设计要求规则,比如阻抗稳定性、同组同层、等长设计等等。今天咱们就来讨论一个由等长而引发的一个设计问题,即绕线设计,如下图所示:

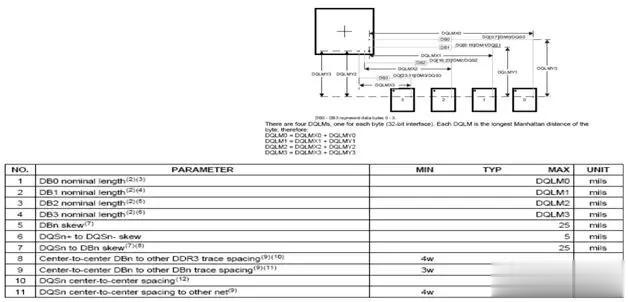

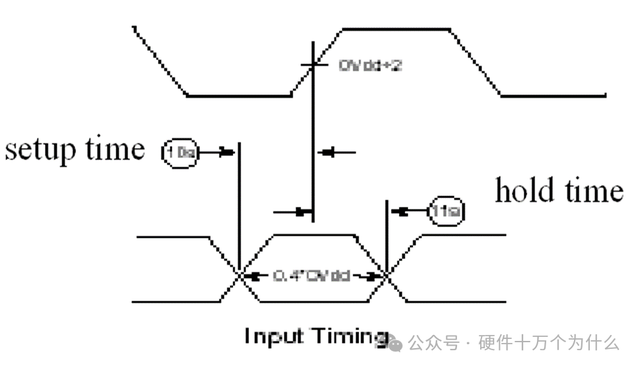

在设计中,特别是DDR3/4/5这类的设计,总会有很多的信号线存在,每一组的数据或者地址控制命令信号线都有一定的等长要求,如下所示为某芯片手册的要求:

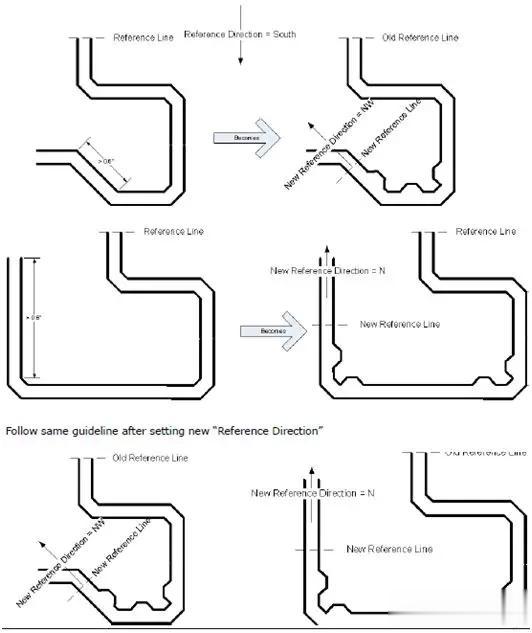

在设计时,当达不到要求时,工程师首先想到的都是绕线,然后还出现了非常多的绕线方式。如下图所示:

PCB(印刷电路板)设计中走线需要绕等长主要是为了保证信号的同步和完整性。这在高速信号传输和差分信号对设计中尤为重要。以下是一些具体原因:

1、时序的要求:

在高速信号传输中,如DDR、PCIe等,数据线和时钟线之间的长度差异会导致信号的延时不同。如果走线长度不一致,信号到达的时间就会不同,可能会导致时钟和数据不同步,造成数据错误。也就是说同步信号系统“有时钟和数据”的系统,需要满足“建立时间”setup time和“保持时间” hold time。

比较早的一些SoC会给出各种时序参数,让工程师自己计算等长的要求,或者计算线长差的要求。

那么时钟和信号线之间就会有延时差要求,现在很多IC已经设计很好了,只需要保持时钟和信号“等长”就可以。

2、同组信号的同步性

在一些对时序要求非常严格的系统中,所有信号需要在特定的时刻到达。如果走线长度不一致,会导致某些信号先到达,某些信号后到达,破坏了系统的时序要求。

对于有些总线来说,数据是一组数据,地址,命令这些也是一组数据,需要组间等长。

3、差分信号对:

对于差分信号对(如LVDS、USB、Ethernet等),两条信号线之间必须保持等长,以确保差分对的信号在接收端保持相位一致。如果两条线长度不一致,会导致信号相位偏移,影响信号传输的质量。

理想情况下,差分信号是正负对称的,其共模份量为零或者只有直流份量,如图所示。如果差分线的正负传输线长度不等,造成传输时间不一致,实际上就是信号在时间轴上的不对称,在终端负载电阻上就能观察到图2所示的波形。显然此时的正负波形不能严格对称,差分电路中的正负电流无法抵消,于是其电源中就有共模电流份量在流动。

研究过EMI的人都知道,共模辐射是最难对付的。

PCB设计:差分线

二、一些需要绕等长的信号

DDR

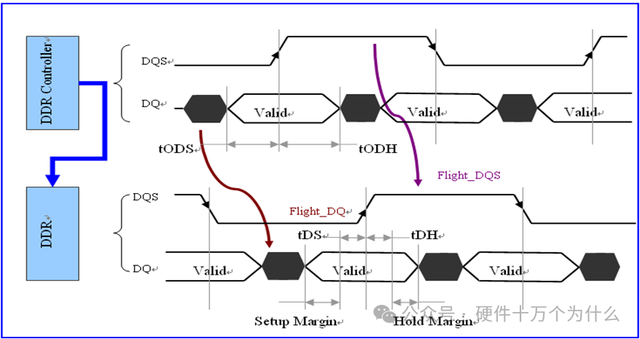

首先可以想到的就是DDR信号(DDR是最常见的源同步传输方式的信号之一),DDR中所有的控制线和地址线都是在CK上升沿与CK#下降沿的交叉处被采样;而数据线与其对应的DQS、DQS#(数据选通)信号同步。

DQS、DQS#为数据选通(锁存)信号,双沿有效,写数据时输入,信号沿与数据中心对齐;读数据时输出,信号沿与数据边沿对齐。

以16bit DDR为例,其一共可以分为三组来做等长处理:

第一组:CLK/CLK#、地址线与所有的控制线

第二组:D0~D7、DQS0、DQM0

第三组:D8~D15、DQS1、DQM1

eMMC & SDIO

其次就是eMMC总线和SDIO总线,在这两种总线中,DATA信号和CMD信号都是与CLK同步。

所以eMMC总线和SDIO总线中DATA信号、CMD信号和CLK信号需要一起做等长处理,支持HS400的eMMC总线还有DATA Strobe信号,也需要和数据线做等长。

RMII、GMII、RGMII、XGMII(MII)

MII是媒体访问控制(MAC)子层和物理层(PHY)之间的接口,从媒体独立接口(Media Independent Interface)一文中我们可知,MII总线一般分为两部分(Tx和Rx),TX数据线与TXCLK信号保持同步;RX数据线与RXCLK信号保持同步。

所以MII总线的等长处理可以分为两组:

第一组:TXD[0:3]、TX_CLK

第二组:RXD[0:3]、RX_CLK

同理,RMII、GMII、RGMII、XGMII都需要分成两组做等长处理。

HDMI

在HDMI 2.1之前,HDMI有三对差分数据线和一对CLK信号,但是这组CLK信号只是作为参考信号,在接收端倍频用于数据信号的采样,传输时并不与数据信号同步。

所以在HDMI2.1之前,只要保证三对数据线绕等长即可(实际根据HDMI协议规定,HDMI 2.0的对间Skew可以允许最大2000mil,就算不绕等长也基本不会有问题)。

而对于HDMI 2.1,由于其采用了时钟数据恢复技术,不会存在时差,所以可以不用绕等长。

三、“等长”≠“等延时”

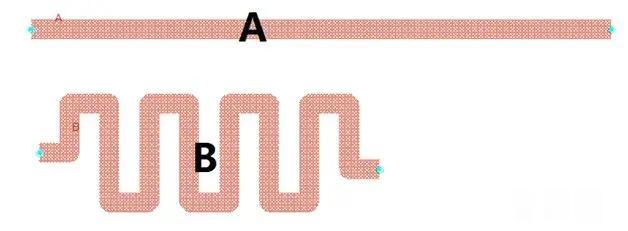

相同物理长度的两段传输线如下图所示,一段直线A,一段绕线B,A和B哪一段的延时会更大?

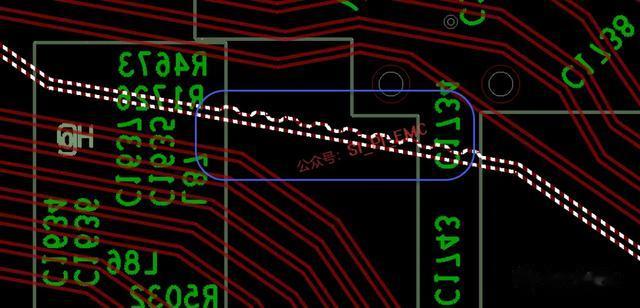

本文就和大家聊一聊平时咱们绕线的方式到底存在一些什么问题?为了完成这个问题的研究,特意做了一个测试板,设计了研究对象为10inch的传输线,一段做参考为直线(上),一段为绕线(下),如下图所示:

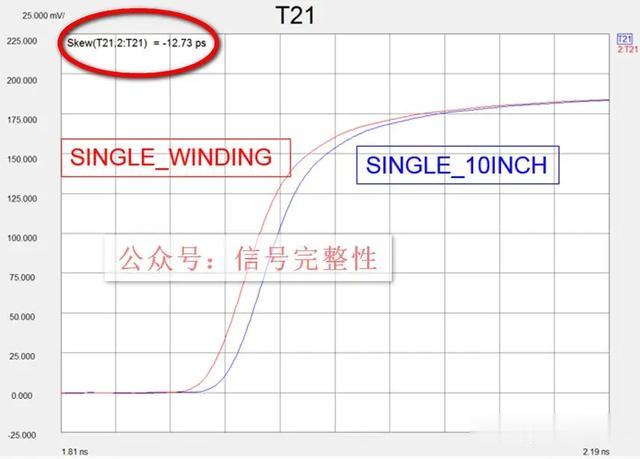

一般,大家通常都会认为,这样已经算等长了,而且是完全等长。但是,通过测量其传输特性,测量的结果如下图所示,我们可以看到,其差异还是不小,相差了12.73ps(红色圆圈),而且绕线比直线传输的更快。

这12.7ps换算成物理长度,约为80mil。80mil的长度应该是让有经验的工程师吓一跳,毕竟平时硬件工程师说:给我做好等长,误差在2mil的时候都会跳起脚来大骂。当然,我们这里做实验设计的为10inch,通常很多布线都没这么长,但是也有一些布线确实非常长的。但是,不管怎么样,这个实验都告诉了我们,物理等长,不等于实际设计就等长了。这也是为什么,近年来,业界一些厂商都提倡时序等长的原因。

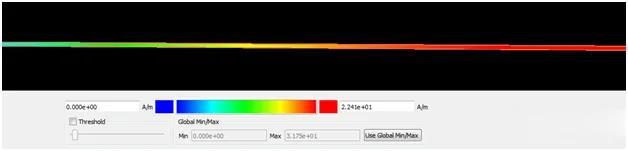

这是为什么呢?原因就在于绕线之后,由于趋肤效应和电磁场效应,信号都是在表面传递。为了解释此现象,在ADS中设计了一段绕线,进行了电磁(EM)仿真,结果如下图所示:

从上图中,我们可以看到,在绕线的地方,都是在相对比较紧耦合处场电流密度比较大,呈红色,在上方(与传输线平行)以及传输线的中心处,电流密度比较小,呈浅色,这就说明信号靠近边沿处传递,这样就导致了信号传递的“更加快速”,所用的时间更少(本来可以给大家放一张动态图的,但是没能做好,有机会的时候,再给大家show一下)。

而直线的仿真结果如下图所示(长度太长,所以只截取一部分):

通过以上的分析即可说明,相同的物理长度,绕线的一段延时更小,这样,我们就能回答前面提出来的问题了,显然是A的延时更大(绕线更快)。

那么问题又来了,工程师在设计时遇到不“等长”的时候,如何做好设计呢?第一,把物理等长的观念改为等时,不管绕线还是直线,需要的是传输延时是一样的。有的PCB设计工具是可以使用时间来表示物理长度的;

第二,有时序关系的信号线,在设计时做到同进同出同设计,尽量减少绕线;

第三,如果某一段传输线确实要绕线,绕线的形状大一点,波与波的距离大一点,或者绕的比直线更长一点,至于绕多长,我也不知道,还是请工程师进行下仿真吧(这就是为什么要进行后仿真了)。

这种绕线的研究,并不是说每一种总线设计都需要这样做,对于一些低速信号、对时序没有特别要求的信号或者对EMI没有特殊要求的项目,工程师可以不用考虑。

本文部分内容参考引用

蒋修国《信号完整性》《等长绕线的影响》

何庆松《差分线的长度匹配问题》龙猫讲电子《什么信号需要绕等长》PCB设计系列文章

【2】硬件工程师要不要自己画PCB

【4】PCB走线应该走多宽?

【6】过孔

【8】死铜是否要保留?(PCB孤岛)

【10】PCB材料、FR4到底是指什么材料?

【12】钢网

【14】PCB布局、布线 的要领

【16】信号的反射

【18】沉金、镀金、喷锡等表面处理工艺

【20】电容的摆放位置

【22】PCB的飞针测试

【24】为什么PCB变形弯曲?如何解决?

【26】PCB的叠层设计

【28】PCB设计中电源处理与平面分割

【30】PCB的介质损耗角是什么“∠”?

【32】晶振为什么不能放置在PCB边缘?

【34】什么是传输线

【36】如何利用PCB散热

【38】纠结:走线之间的GND保护地线要还是不要?

【40】进行 PCB 设计时应该遵循的规则

【42】除了带状线、微带线,还有“共面波导”

【44】PCB设计时,板边为什么要打地孔

【46】为什么要把参考平面掏空?

【48】用EMC思想来设计DC/DC电源的PCB

【50】为什么要把过孔堵上“导电孔塞孔工艺”

【52】PCB板上的Mark点【54】刚柔板(软硬结合板)

【56】PCB设计中电容的摆放

【58】去耦电容在PCB设计中的布放与走线

【60】PCB设计checklist:电源

【62】PCB设计checklist:高速数字信号

【64】PCB设计:金手指

【66】DDR4的PCB设计及仿真

【68】什么是好的“PDN”的PCB设计

【70】USB2.0 PCB布线

【72】PCB设计,焊盘与过孔工艺规范

【74】PCB 过孔对散热的影响

【76】为什么有时在PCB走线上串个电阻?有什么用?

【78】PCB设计不好造成的信号完整性问题