摘 要:QFN封装器件在组装过程中容易出现信号焊盘桥连、散热焊盘空洞和侧面焊点爬锡高度不足等工艺缺陷。本文分析了缺陷形成机理,并从PCB焊盘设计、焊膏印刷模板设计提出了有效预防措施。

关键词:QFN封装;桥连;空洞;电子组装

0 引言

方形扁平无引脚(Quad Flat Non-Leaded:QFN)封装具有小型化、轻量化、高散热性和电气性能,能够满足军民领域电子产品对小型化、轻薄化、高性能的发展需求,尤其是手持式产品[1-3]。QFN封装近似CSP塑料封装,但封装底部无焊球,封装周围也无翼型外伸引脚,通过在印制电路板焊盘上印刷焊膏,进行再流焊焊焊接形成焊点,实现与印制电路板的机械与电气连接。

由于QFN封装器件焊点高度较低,IPC-7093指出在焊接过程中QFN封装类底部端子器件的焊接质量的工艺关键控制点为焊点的高度和散热焊盘底部焊点的空洞率[4-6]。目前, QFN封装器件引脚向超细间距发展,典型值为0.4 mm,甚至0.3 mm,底部焊端由单排向双排、多排方向发展,这给QFN封装器件的组装工艺带来了极大的挑战。本文将对QFN封装器件组装工艺缺陷类型及形成机理进行分析,并提出解决措施与方法。

1 QFN封装器件特点

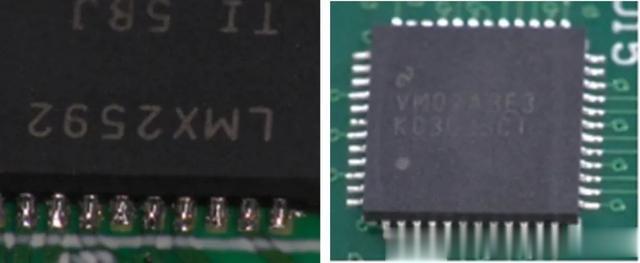

QFN封装采用微型引线框架(Micro Lead Frame)铜基板的封装形式,引线框架直接裸露在封装底部作为焊端,为一种无引脚封装形式,如图1(a)所示[7],图1(b)为QFN封装三维示意图。器件外形一般为正方形或矩形,封装底部中央通常有一个大面积裸露的散热焊盘,围绕散热大焊端周围为矩阵排列的小焊盘,为内部裸芯片提供电气连接,通过再流焊工艺可实现QFN封装器件与PCB焊盘的连接,如图2所示。

图1 QFN封装器件实物图及封装三维示意图

图2 QFN封装器件焊接至PCB板横截面示意图

从图2的QFN封装可知,该类器件内部裸芯片通过引线键合与焊盘相连,具有非常低的自感和阻抗系数,具有卓越的电气性能,可满足高速或微波应用场景。在组装过程中,器件中央大面积焊盘直接与PCB板上的散热焊盘焊接,热阻抗低,具有优异的散热性能,并保证很小的接地电阻。

2组装工艺缺陷及形成机理分析

2.1 超细间距信号焊盘容易桥连

QFN焊盘为一个平面,离器件封装底面高度为0~0.05 mm,几乎与底面齐平,其与PCB对应焊盘构成了“面—面”连接。器件底部具有一个较大的中央散热焊盘,由于焊膏表面张力的作用,散热焊盘焊点高度决定了四周信号焊盘的焊点高度,可通过控制PCB板散热焊盘上印刷的焊膏体积量来调整器件焊点高度。尤其是对于四周为超细间距值(0.3 mm和0.4 mm)焊盘的QFN封装器件,焊膏印刷量要求更为精确,不然会造成桥连缺陷。印刷量过多,会造成贴片后焊膏图形面积扩展,甚至造成器件漂浮,导致相邻焊盘容易发生桥连,甚至开路;印刷量过少,散热焊盘上过少的焊膏体积量导致器件过分塌陷,造成四周信号焊盘焊点的塌落扩展而桥连。图3所示为QFN封装器件贴片焊接后焊点桥连的X-Ray检测图。

图3 QFN封装器件焊点桥连X-Ray图

2.2 大面积散热焊盘易出现空洞

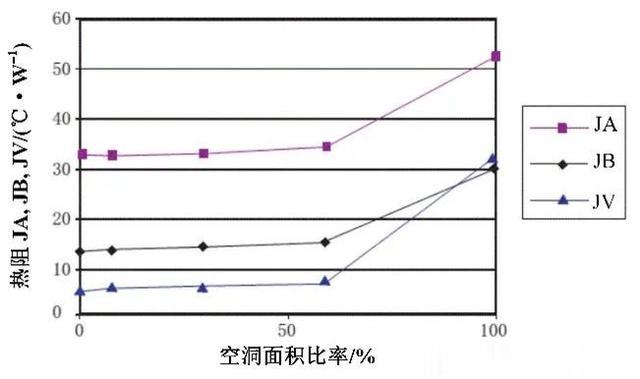

由于QFN封装自身的特点,底部中央包含一个大面积散热焊盘,控制焊点空洞非常困难,且焊点为“面—面”连接,焊盘离封装底面高度低,再流焊焊接时,焊膏中大量的溶剂难以挥发,容易包裹在熔融的焊料中,待冷却后便形成焊接空洞,如图4所示。一般而言,QFN底部散热焊盘焊点空洞面积总和小于焊接面积50%,不会造成器件散热和电气性能的衰减,也不会造成周围小焊盘的可靠性,如图5所示,为IPC 7093中散热焊盘空洞面积比率与散热性能的关系图[5]。然而,当焊点单个空洞最大尺寸大于散热焊盘中通孔间距时,空洞将对高速和射频信号产生巨大影响[8,9]。

图4 QFN散热焊盘大面积空洞

图5 QFN散热焊盘空洞对散热影响图

2.3 侧面焊点爬锡高度不足

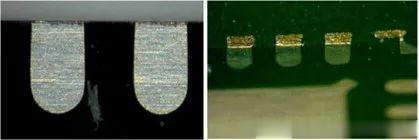

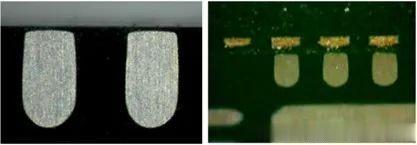

QFN封装器件的分割方式有两种,分别为冲压分离和切割分离。其中切割分离封装形式可进一步分为全引脚封装和引脚内缩封装。全引脚封装为整个引脚厚度外露在封装本体侧面,如图6(a)所示为QFN全引脚封装器件的底部和侧面实物图;引脚内缩封装底部有半刻蚀底部引线框,导致只有引脚厚度的上半部分外露在封装本体的侧面,如图6(b)所示为QFN内缩引脚封装器件的底部和侧面实物图。

(a)

(b)

图6 QFN全引脚分子和引脚内缩封装

由于QFN器件的底部引脚在出厂前会进行电镀处理已确保其可焊性,而封装电镀后要经历切割工艺,所以外露的引脚切口是未电镀,引脚切口的铜在存储过程中容易被氧化,因此在再流焊时无法充分润湿存成不上锡情况,导致引脚趾部无填充,如图7所示。虽然IPC 7093和IPC A 610中对焊点侧面的爬锡高度没有明确要求,为了保证军用电子产品的高可靠,要求QFN侧面焊点能够100%上锡,从而可获得稳定可靠电气性能和机械性能[10, 11]。

图7 QFN封装器件引脚侧面不上锡

3 组装工艺缺陷预防措施

由上分析可知,QFN封装器件组装工艺缺陷主要有信号焊盘容易桥连、散热大焊盘容易出现空洞及侧面焊点爬锡高度不足,造成的因素有PCB焊盘设计、焊膏量、焊膏助焊剂活性、再流焊环境和间隙高度等,需要协同设计。下面将从焊盘设计与焊膏印刷模板设计提出有效预防措施。

3.1 PCB焊盘设计

QFN封装焊盘设计主要包括周围信号焊盘设计、中间热焊盘及过孔设计和PCB阻焊层结构设计。

(1)周围信号焊盘设计

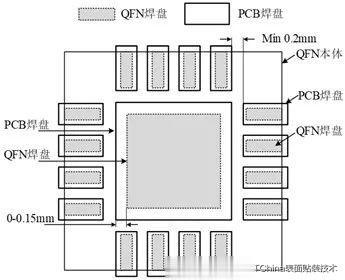

PCB焊盘的设计应比QFN封装器件引脚焊端稍微大一些,焊盘宽度范围一般在0.25~0.5 mm,焊盘长度范围一般在0.6~0.96 mm。为了保证信号焊盘引脚趾部形成填充,焊盘应外延0.1~0.2 mm,内延大于0.05 mm,则必须保证引脚焊盘之间及与中央散热焊盘保留至少0.2 mm的间隙,以免引起桥连,如图8所示。针对细间距QFN器件,PCB上的信号焊盘与引脚焊端宽度设计值应相同,阻焊层设计为开通窗,可进一步降低周围信号引脚焊点的桥连。

(2)散热焊盘及散热导通孔设计

因为QFN封装器件底部具有大面积散热焊盘而具有优秀的散热性能,为了将热量从器件传导至PCB板,PCB板上应设计与之匹配的散热焊盘和散热导通孔。相对QFN底部暴露散热焊盘,PCB板上的散热焊盘各边应向外延0~0.15 mm。中央散热焊盘与周边信号焊盘要保证合理的间隙值0.2 mm,以防止与信号焊盘的焊点桥连,如图8所示。

图8 QFN封装器件PCB焊盘设计

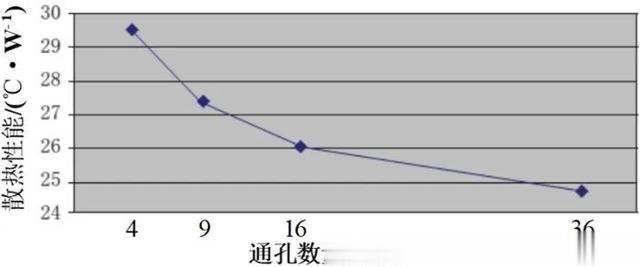

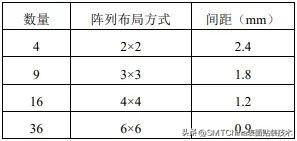

为了充分利用QFN封装器件底部散热焊盘的散热性能,在PCB散热焊盘中通常将设计散热导通孔,并连接到接地平面。导通孔直径一般为0.2 mm~0.3 mm,孔壁镀有1oz的铜,间距为1.0 mm~1.2 mm,散热导通孔的大小及数量与QFN器件散热焊盘大小、功耗及电气性能相关,一般建议开孔面积率在40%~60%[12]。虽然增加导通孔数量可以改善器件的散热性能,但导通孔数量增加到一定值后并不会显著提升其散热性能,如图9所示,尺寸为7×7 mm,48引脚封装QFN器件散热通孔对热性能的影响曲线图,导通孔设计参数见表1所示[5]。

散热通孔还可作为焊膏熔化后助焊剂的挥发通道,降低散热焊盘上的空洞。为了防止在再流焊过程中通孔渗锡,对通孔可采用阻焊处理。阻焊处理一般有三种方式,使用干膜阻焊在通孔的顶部或底部,使用液态感光阻焊膜对底部进行填充。相关研究表明,底部阻焊或填充方式由于排气产生较大的空洞而覆盖超过两个以上的导通孔,采用顶部阻焊可产生较小的空洞,后期可通过模板避孔的设计方式避免通孔阻焊层对焊膏印刷影响,一般阻焊膜的直径比通孔直径大100 μm左右[7]。

图9 通孔数量与器件散热性能的关系图

表1 导通孔布局设计参数表

3.2焊膏印刷模板设计

由于QFN封装器件周围信号引脚表面积小,只能通过PCB板上焊盘印刷的焊膏来保证焊点的可靠性,其封装底部中央的大面积散热焊盘离引脚内边缘很近又增加了难度。前文建议的焊盘设计可以解决一些表面组装工艺问题,但模板设计与焊膏印刷质量也很重要。

(1)周围信号焊盘模板设计

QFN封装器件周围信号焊盘最优和最可靠的焊点高度为50~75μm,其模板的设计至关重要,开孔应让焊膏具有最大的释放量。为了达到最佳的焊膏释放量,模板设计时主要满足面积比和厚宽比,要求其值分别大于0.66和1.5,模板开孔与PCB焊盘尺寸应为1:1,当选择内缩引脚封装时,由于可焊面积减小,模板开孔尺寸可相应减小。针对细间距引脚,尤其是0.04 mm的QFN封装器件,可适当减小模板开孔以杜绝相邻引脚的桥连。

(2)散热焊盘模板设计

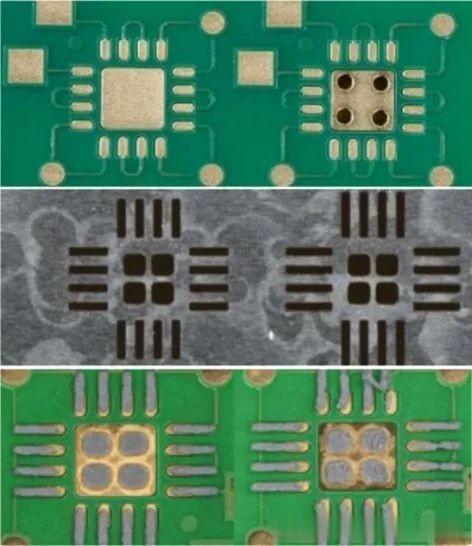

由前文分析可知,散热焊盘焊膏覆盖面积太大,容易导致空洞,飞溅、锡球等焊接缺陷。为了减少散热焊盘焊膏印刷量,其模板设计建议设计多个小开孔来代替一个大的开孔方式。开孔形状可以是圆形或方形,采用阵列布局,典型的焊膏覆盖率要求达到50%-80%。如图10所示为某QFN封装器件的QFN封装器件焊盘设计、钢网设计及焊膏印刷图。

图10 QFN封装器件焊盘设计、钢网设计及焊膏印刷

(3)模板类型及厚度

模板应使用不锈钢材料,耐用且变形小,通过激光切割和电极抛光,(纳米钢网),可提升模板侧壁光滑度,有助于焊膏的释放并减少空洞。开窗应做成梯形结构,确保焊膏均匀脱模,减少拉锡,并有助于器件贴放。针对引脚间距≤0.5mm的QFN封装器件,建议使用0.12mm厚度的模板,更大引脚间距建议使用0.15mm厚度的模板。文献10中研究表明,印刷的焊膏量对周围信号引脚焊点爬锡高度影响最大。可对QFN封装器件的侧面引脚进行预上锡,再流焊焊接过程中加氮气保护,可显著提升引脚的爬锡高度,如图11所示。

图11 侧面焊点100%爬锡

4 结论

由于QFN封装器件其优越的性能,已在电子产品中广泛应用,但其采用微型引线框架无引脚封装及大面积散热焊盘的特点,对组装工艺带来了极大的挑战,在组装工艺过程中容易出现桥连、空洞及侧面焊点爬锡高度不足等缺陷。本文分析了缺陷形成机理,从PCB焊盘和焊膏印刷模板设计提出了预防措施,从设计方向提升电子产品的可制造型。