爱普生宣布开发出独特的宽幅度LVDS输出 —可灵活选择与LSI -相匹配的低噪声输出

精工爱普生公司(TSE: 6724,“爱普生”)开发了一种新的晶体振荡器差分输出方案。新方案,宽幅低压差分信号(WA-LVDS),可以灵活选择最适合LSI所需的幅值水平的输出。爱普生计划在2025财年(从2025年4月开始)将WA-LVDS输出晶体振荡器商业化。

随着数字化的进步,数据流量正在迅速增长,第五代移动通信系统(5G)、物联网(IoT)和下一代通信系统将需要更快的传输速度和更高的容量来支持这些流量。在这种系统中,数据传输需要LVDS、LV-PECL和HCSL等通用差分输出。每一种方案都有自己的特点,工程师们会为他们的特定系统选择最好的方案。然而,近年来,通信设备对性能的要求越来越高,这意味着现在正在设计电路以接收通信设备中使用的lsi的最佳差分输出。因此,通用差分输出不能在越来越多的情况下使用。因此,对适合lsi的差分输出的需求预计将在未来更加强劲。

现有的具有通用差分输出的LVDS具有比LV-PECL和HCSL更低的电流消耗。然而,另一方面,它也具有较低的幅值,因此抗噪能力较差。为了解决这个问题,爱普生开发了WA-LVDS,这是一种具有可选择幅度水平的差分输出,可以灵活使用。WA-LVDS通过使其易于获得高振幅而增加了抗噪性。它还提供比LV-PECL和HCSL更低的电流消耗。

作为晶体器件的领导者,爱普生将继续提供满足各种电子设备和社会基础设施需求的晶体器件产品。

*:差分输出是一种信号传输方法,其中数据传输为极性相反的两条独立线路之间的电压差。差分输出的优点是数据传输频率高,抗噪能力强。

附录

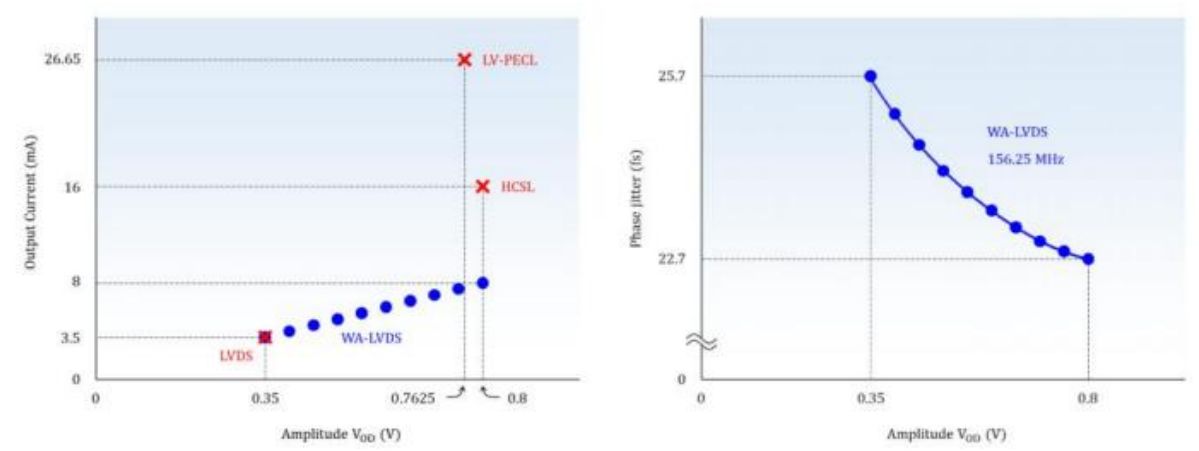

振幅、输出电流和相位抖动*差分输出量如图1和图2所示。LVDS、LVPECL和HCSL用红色表示。WA-LVDS是蓝色的。

图1

LVDS的H和L水平对应于振幅的差值定义为0.35 V。虽然输出电流较小,但振幅较低,导致LVDS的抗噪性低于LV- PECL和HCSL。另一方面,LV-PECL和HCSL的振幅较大,但消耗了大量的电流。WA-LVDS的振幅可以以较小的增量 进行选择,从与LVDS相同的水平到与LV-PECL和HCSL对应的水平。此外,WA-LVDS输出电流保持在较低水平,导 致低电流消耗。

图2

随着WA-LVDS振幅的增加,相位抖动减小,导致低噪声的差分输出。

图1:振幅vs。差动器的输出电流图2:WA-LVDS相位抖动

相位抖动:时钟周期的波动称为抖动。相位抖动是对无抖动理想时钟的边缘偏差的度量,可以从相位噪声特性计算 出来。