硅光子学在许多高科技领域都广为人知,但获得高质量技术的机会仅限于于其垂直的领域,或拥有大量资源参与大批量晶圆厂的工厂。

随着多项工艺设计套件和多项目晶圆计划被公布,门槛从而被降低,MPW服务由一流的工艺设计套件(PDK)提供支持,该套件允许设计人员布局并获得在首次运行时正常工作的光子集成电路(PIC)。

这些电路的制造在纽约州立大学理工学院进行,该学院运营着一个世界级的300毫米洁净室,除了硅光子学外,还开发了7纳米以下的CMOS架构。

该设施及其设备的工业级管理提供了高质量的光子器件,这些器件在运行之间可重复,并具有快速的周转时间,这些器件的性能可与最先进的器件相媲美,并可实现各种硅光子应用。

在过去的二十年中,硅光子集成电路(PIC)的普及随着其报告性能的提高而增加,这种普及部分是由于硅基PIC相对于替代材料平台(即III-V)具有潜在的成本效益。

具体而言,使用硅基平台制造的PIC能够利用硅基电子集成电路(IC)无与伦比的基础设施,在许多情况下,为大批量硅IC建立的相同制造设施(“晶圆厂”)、工艺设备(“工具”)、化学品、材料和供应链可以应用于PIC。

此外,硅晶片的原材料成本明显低于用于晶圆,凭借成熟的基础设施和较低的启动成本,因此硅基PIC是一个有吸引力的商业化平台。

硅PIC主要为电信和数据中心通信市场批量生产,这些产品由大型商业硅代工厂制造,这些代工厂需要大型制造协议,以证明工艺开发和晶圆厂时间的合理性。

电信/数据通信应用能够清除这一障碍,而硅光子学的大多数早期应用(自由空间通信、激光雷达、生物/化学传感、量子计算等)都受到这一高进入门槛的限制。

相反,这些应用领域的研究人员或初创公司必须在规模较小的晶圆厂工作,这些晶圆厂可能无法利用大批量硅晶圆厂的规模经济。

弥合封闭的大批量晶圆厂和较小的精品晶圆厂(或学术实验室)之间的差距的是更大的研发联盟,如IMEC,CEA-Leti和(在美国)纽约州立大学理工学院的美国制造集成光子学研究所。

这些组织中的每一个都运营着多项目晶圆(MPW)服务,将通过分担其最先进的洁净室设施中的开发和制造成本来访问硅光子集成电路。

AIM光子学

“AIM光子学”成立于2015年,前身是美国制造集成光子学研究所,是由美国联邦政府,一些州政府和成员公司资助的制造创新研究所。

AIM光子学的使命部分是“推进集成光子电路制造技术的发展,同时提供最先进的制造,封装和测试能力”。

除了标志性的MPW计划外,AIM还资助了全国成员大学的各种研发项目,并在纽约州罗切斯特推出了首个光子学测试,组装和封装(TAP)设施,AIM光子的MPW服务和TAP设施是世界上唯一使用300毫米晶圆先进工具运行的设施。

工艺设计套件

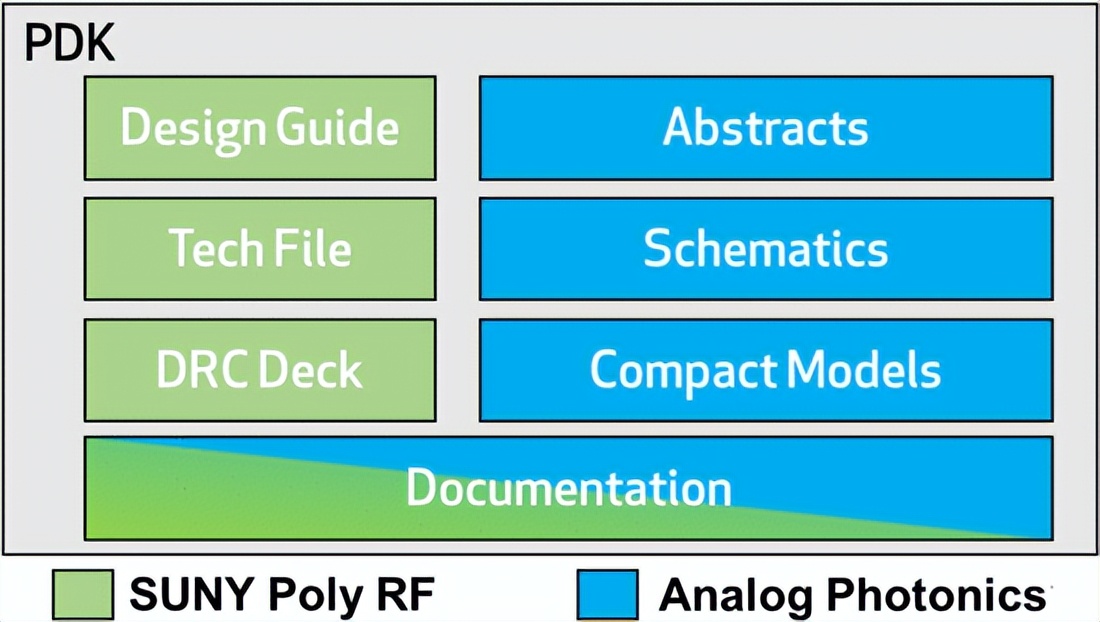

在纽约州立大学理工学院制造的AIM光子学MPW程序由模拟光子学生产的广泛工艺设计套件实现。

模拟光子学(AP)利用SUNY-Poly晶圆厂和硅光子学技术的多年经验,提供已在晶圆上验证的器件,纽约州立大学保利分校提供的信息包括设计指南、技术文件和设计规则检查(DRC)幻灯片,这些材料将提供有关铸造工艺的充分信息,以进行设计、布局和流片。

设计指南包括掩模层名称、类型(负或正)、不透明度、厚度、用途、应力梯度和公差,指南将用于设计意图层传输到可制造的层编号,并显示这些层之间的交互。

由此映射出将设计转换为设计规则校验(DRC)卡片组可识别的图形数据库系统(GDSII)或OASIS文件格式。

尽管基元元素足以用于自定义设计流片,但功能齐全的设计需要流程、设计、测试和布局方面的专业知识。

因此,光子设计通常需要多次制造运行(迭代)才能满足某些规格,这增加了开发成本并减慢了产品开发的速,增加的成本和开发时间可能导致定制设计带来的竞争优势丧失。

相反,首选PDK组件库辅助设计来准确预测PIC行为并快速迭代,从而降低风险并缩短上市时间,许可组件库的总体成本可能低于这些组件的自定义开发。

PDK元件库通常包括摘要、原理图和紧凑模型,摘要允许PDK开发人员阻碍包含设计IP的真实几何形状的部分,同时使用户能够与组件的指定光学和电气端口进行交互。

然后将摘要替换为真正的几何形状,以便在经纪人或铸造厂制造准备好的文件,这些组件的原理图和紧凑模型用于预测设计的性能,包括定制设计的元素。

当前的APSUNYPDK组件库提供了最先进的可验证性能和高产量,并包括原始元素和组件库的文档,这些文档指导设计人员有关PDK层次结构、更改、设计方法、支持的EPDA工具、组件库性能、应用说明和说明(PDK的安装、许可和流片)的信息。

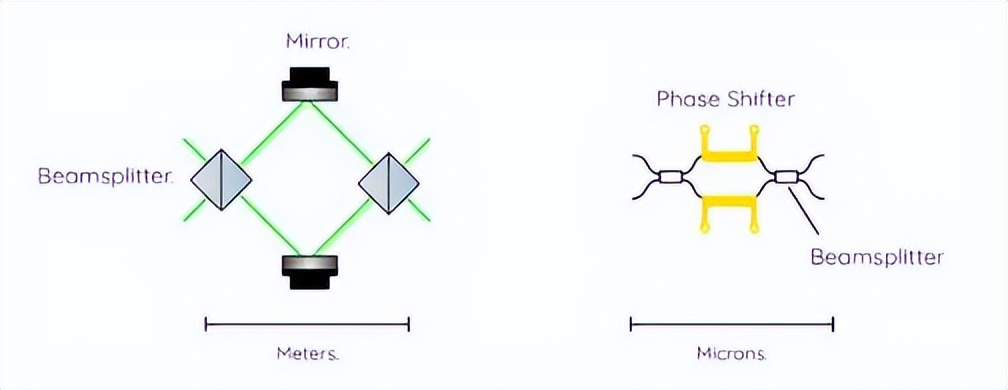

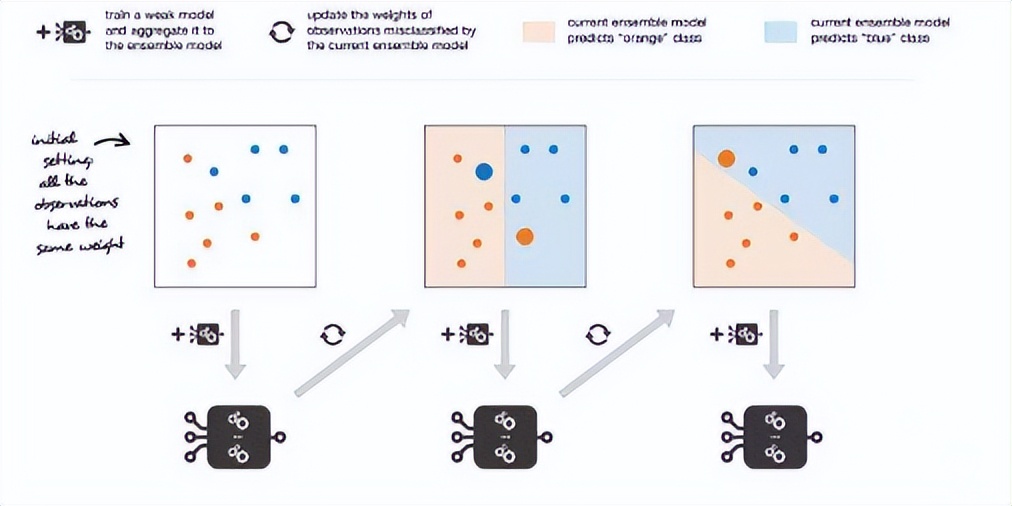

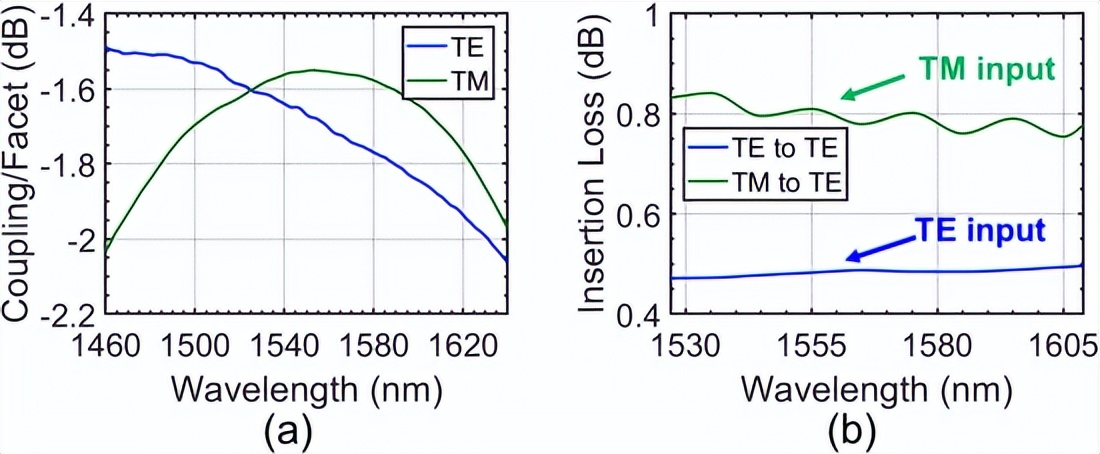

而APSUNYPDK中的无源器件包括垂直和边缘耦合器,分路器,交叉,定向耦合器,层间过渡(硅到氮化硅波导)和极化旋转器/分路器。

有源器件库的亮点包括高速开关、微盘调制器、马赫曾德尔调制器和光电探测器。

PDK分为专为O波段或C波段和L波段应用设计的元件,支持数字和模拟电路架构,APSUNYPDK专为MPW程序而设计,因此为使用该程序的各种应用程序提供支持。

为此,只有不断开发和实施新设备,用以将PDK/MPW的使用扩展到数据通信/电信之外,并扩展到RF,5G,生物/化学传感器,量子计算,LiDAR等应用。

公共工程部服务

AIM光子学MPW的制造运行由加利福尼亚州玛丽娜德尔湾服务汇总,该服务还托管和分发PDK,并运行最终设计规则检查(DRC)。

需要MOSIS在制造运行之前进行,以便晶圆厂有时间审查DRC结果,让MOSIS从PDK组件库中插入IP模块并组装设计,让掩模室制造标线。

这些流程大约需要30-40天,具体取决于在DRC期间发现的可能需要重新设计的问题,一旦掩模到达晶圆厂并且晶圆开始进入生产线,制造过程大约需要90天才能制造出完整的晶圆制造后,每个晶圆都要经过最终的质量保证检查和测试。

然后将晶圆切成丁,并将芯片分发出去,这项工作大约需要3-4周,这使得有源硅光子学MPW运行的周转时间从设计下降到交付芯片的周转时间达到150天。

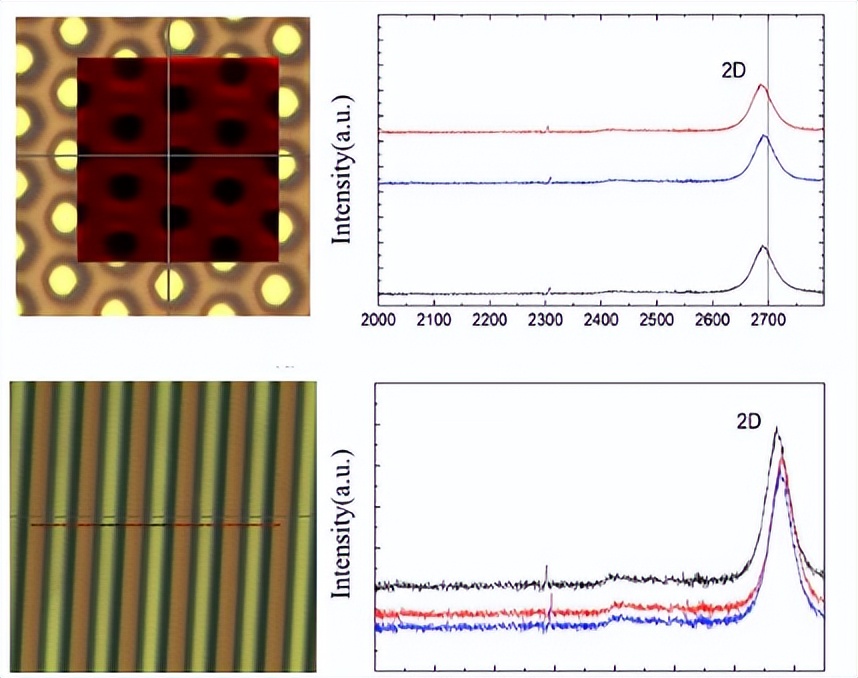

SOI使用多个掩模进行图案化,以创建变薄的硅并定义全厚度硅,行业标准的浸没式光刻技术用于定义晶圆上的硅图案,关键尺寸控制低至100时,水平间错位可忽略不计。

高级反应离子蚀刻(RIE)用于获得几乎垂直的侧壁,后蚀刻化学处理产生超光滑的侧壁,图案化硅使APSUNYPDK的硅波导,耦合器和各种其他无源元件成为可能。

此外,硅能级构成了有源组分的基础,图案化的硅用低损耗介电包层材料掩埋,例如等离子体增强正硅酸四乙酯(pTEOS)。

具体而言,非保形沉积用于最大限度地减少可能导致缺陷的电介质夹断,两个低损耗氮化硅(SiN)波导电平可供设计人员使用,其制造方式与硅波导类似。

值得注意的是,使用独特的低温等离子体增强化学气相沉积(PECVD)SiN,以实现SiN波导与有源组件的共集成,与硅波导一样,RIE图案化和后蚀刻处理已经过优化,以产生低损耗波导,然后用pTEOS包覆。

PDK根据设计人员的应用提供不同类型的光电探测器,所有这些都基于二极管,这些二极管是在TEOS的光刻定义沟槽中制造的。

锗通过CVD生长,具有专门调整的生长速率和温度,以最大限度地减少材料的缺陷,然后对Ge进行平面化、封盖并定义顶部接触面积,与Ge的触点由CMOS兼容材料制成,这些材料专为优化探测器性能而选择。

最终的工艺模块是一个深沟槽,以促进低损耗边缘耦合,深沟之后,晶圆被送到外部供应商进行切割,单个芯片将被运送出进行测试。

除了上述工具、工艺、生产线和集成控制和监视器之外,要在每个MPW晶圆制造过程中都对其进行多次测试和检查,以增加质量控制。

在每个金属级别进行电气测试,以测量与CMOS相关的标准参数,并确认有源光子学组件的基本行为。

最后,在关键步骤,包括在制造流程结束时,手动和自动检测都用于检查随机缺陷以及评估晶圆质量,未通过晶圆验收标准的晶圆是不能被送出使用的,任何具有不可接受的缺陷尺寸或数量的芯片都将被排除在切割计划中。

APSUNYPDK中的无源元件包括波导、边缘耦合器、垂直耦合器、1%和10%功率抽头、3端口和4端口分路器、层过渡(自动扶梯)、偏振旋转器、偏振分路器/旋转器和波导交叉。

硅和氮化硅波导的使用是该PDK的独特之处,对于支持低PIC到光纤耦合损耗、不同工作波长下的低传播损耗、小弯曲半径、低偏振依赖性以及从光学计算和互连到传感器和非线性光学器件等应用的有源功能至关重要。

除了标准的硅和氮化硅波导外,还提供低损耗硅波导,在0至8的波长范围内具有1.05–1460,较长波长下波导损耗的增加与与波导边缘的相互作用增加非常吻合。

APSUNYPDK中的波长选择组件包括4通道可调谐和谐振波分复用微盘开关、微盘调制器和微环滤波器,它们在C波段共享相同的自由光。

AIM光子学研究所通过纽约州立大学理工学院的300毫米制造设施组装了最先进的多项目晶圆(MPW)服务,并由模拟光子学开发的工艺设计套件提供支持。

制造工艺流程和APSUNYPDK中,有一个全面的有源和无源硅光子学库,可提供经过验证的先进性能,并支持具有CMOS兼容电压的各种硅光子学应用。

借助成熟的PDK及其集成的电子光子学设计自动化软件支持,进一步简化了光子系统的设计过程,大大减少了违反设计规则的次数,从而降低了设计师和制造设施的时间成本。

未来的PDK更新将侧重于进一步提高组件性能,并提供经过验证的子系统性能,以进一步缩短上市时间。