前沿导读

台湾国家科学委员会(Taiwanese National Science Council)主席吴成温,在台湾立法机构的简报会上表示,在半导体制造方面,中国大陆的企业可能落后于中国台湾的台积电十年。

在此之前,他被问及媒体报道称华为旗舰手机的出现,表明中国已经设法赶上了其芯片制造技术。对此,吴主席分享说,由于台积电领先的 2 纳米半导体技术计划于 2025 年投入量产,因此根据他的估计,中国台湾和中国大陆的差距应该超过十年。

技术差距

在华为的麒麟芯片回归之后,国内外的技术机构通过拆解分析得出结论,该芯片是采用了中国国产技术制造的7nm芯片。麒麟9000S、9010、9020均是中国晶圆厂商基于Fin FET技术,通过多重曝光和多重图案化,实现N+2的制造工艺,等效7nm水平。

对于这些新的国产手机芯片,吴成温表示:全球领先的芯片制造商台积电,已准备好在明年使用 2 纳米技术制造芯片。从制程技术的角度来看,大陆的芯片制造水平要比台湾的芯片制造水平落后10年,甚至更长的时间。

台积电的7nm技术,正式量产的时间为2018年,分为DUV技术和EUV技术两种制造工艺。在EUV光刻机全面铺开之后,台积电的7nm工艺以及未来更先进的制程工艺,均放弃了DUV技术,采用EUV。

芯片的核心是Fin FET技术,鳍式场效应晶体管。

晶体管的内部分为源极、漏极、栅极,源极和漏极在两边,栅极在中间。

外部施加相应的电压,电流进入晶体管之后,会在源极和漏极之间的电流沟道中流通,栅极起到控制电流通过的作用。电流通过,二进制数为1,电流关闭,二进制数为0。

电流的通过和关闭,代表了1和0的二进制数转换,正是因为这种电流的二进制转换,晶体管才可以释放出制定的电子信息来驱动芯片释放系统算法。

栅极控制电流的精密程度,直接决定了芯片的性能释放和功耗高低。如果出现漏电的情况,那么会造成芯片的功耗增高,伴随而来的就是大面积的发热。

而Fin FET技术,就是将晶体管内部的栅极进行3D化凸起,三方面包裹电流沟道,拥有更加优秀的电流控制能力。

Fin FET技术是全球芯片产业的核心设计方案,也是唯一的设计方案。

台积电的第一代Fin FET技术,出现于2013年开发的16nm制程工艺。并且台积电在后续的发展当中,一直在不断地打磨Fin FET技术,制程工艺也从16nm推进到12nm,然后推进到7nm、5nm、3nm等更加先进的水平。

中国晶圆企业的Fin FET技术,最早出现于2017年,也就是梁孟松来到中国企业的这一年。但是实现大面积的量产的时间,则是在2020年左右,上海晶圆企业给深圳的手机厂商代工了麒麟710A,该芯片采用了基于Fin FET技术的14nm工艺制造。

如果从晶体管技术的量产时间上面来看,中国大陆的芯片制造业确实要落后于中国台湾地区10年以上的时间。况且中国大陆地区的企业还无法拿到先进的制造设备,更加拉开了双方之间的差距。

以上是从晶体管的技术角度来看待大陆和台湾产业的差距,下面来说在制造技术上面,大陆和台湾地区各自的优势。

制造技术

台积电是国际上面第一个实现晶圆厂革命的企业,甚至创始人张忠谋还打出了“虚拟晶圆厂”的概念。所谓的“虚拟晶圆厂”,就是告诉合作的芯片设计企业,将台积电的制造工厂当做自己的工厂看待,有什么需求、有什么需要对接的技术问题,可以直接提出来,双方一起解决。

这种“虚拟晶圆厂”的产业模式,让台积电获得了来自于全球芯片产业的商业支持,将许多顶尖的技术设备全部优先交付给台积电。

在美国EUV LLC技术联盟冲击EUV技术的过程中,台积电、英特尔、三星等企业纷纷给ASML注资,确保其拥有充足的设备研发资金。同样的,台积电、英特尔、三星也获得了优先采购产品的权力。

台积电的第一代7nm工艺,采用的依然是DUV光刻机,通过多重曝光和双重图案化的方法制造。包括现在中国晶圆企业给华为制造的麒麟芯片,也是如此。

多重曝光和多重图案化是因果关系,设备第一次曝光之后,光刻胶会记忆之前的曝光参数,即便第二次曝光与第一次曝光是分开进行,但是依然对曝光的图像没有影响,这时候就需要多重图案化技术的介入。

所谓的多重图案化,简单来说就是每次曝光之后进行图案化技术,一直到刻蚀、剥离光刻胶,并涂上新一层光刻胶以接受下一次的曝光。在EUV技术没有大规模使用之前,这种多重图案化技术是国际主流的制造技术。

多重图案化的一个关键步骤是刻蚀,相应的刻蚀偏置,可以提高图像分辨率,但前提是要有足够精准的套刻精度和晶圆台精度。

多重图案化有4个技术节点,但是每增加一层图案,相应的光刻技术和刻蚀技术的成本便会增加一倍。每增加一个分离层,套刻的精度就会变差一些。

假设套刻精度为CD的1.5%,如果套刻精度的误差没有进行优化,这个对准的实际误差可能会差到6阶。数值计算下来,是CD的8.4%,这个精度的误差情况是非常严重的,直接影响了产品的整体良品率。

台积电也只是用了一代DUV的多重图案技术,随后便转向了EUV光刻技术。其中的原因有两个:

1、DUV设备的多重图案化技术成本很高,而且需要长时间的技术磨合来解决良品率的问题。越往后发展,这个问题越严重。

2、EUV设备已经研发完成,虽然设备的采购成本比DUV高出许多,但是随着后续技术和产业的发展,EUV的成本会随着消费产品的供应而逐步下降。而DUV设备,继续向下发展的空间小,并且成本和良品率也无法预测,从长远角度来说,EUV的技术价值远高于DUV。

台积电可以切换EUV工艺,但是中国企业不行。

中国芯片产业能拿出的最好制造设备,也只是曾经从ASML采购的1980i和2000i DUV光刻机。想要发展7nm的先进制程工艺,只能走多曝光和多重图案化技术这一条路。

根据国际权威机构的技术分析显示,麒麟9000S、9010、9020在制程技术上面的提升不算大,依然是之前的N+2工艺,但是升级优化的水平是有目共睹的。

还有一点要重点提出来,多曝光的双重图像技术,会从光刻机当中损失至少40%的产能。

解决这个问题的方法,就是在光刻机上面,额外添加一个掩模扫描台,让光刻机实现双掩膜台工作。这种双掩模台的光刻机,需要专门定制。

这种双掩模的光刻设备,可以有效的让多重曝光的成本和良率达到平衡点,但是对多重图案化技术无效。

很可惜,中国并没有双掩膜台的光刻设备。就算有这种设备,也无法降低手机芯片的制造成本。

现在能说明情况的是,国产技术已经解决了多曝光和多重图案技术的良品率问题,达到了台积电在2019年所达到的制造水平。并且国产技术在打磨多曝光和多重图案化技术上面,比台积电更加优秀。

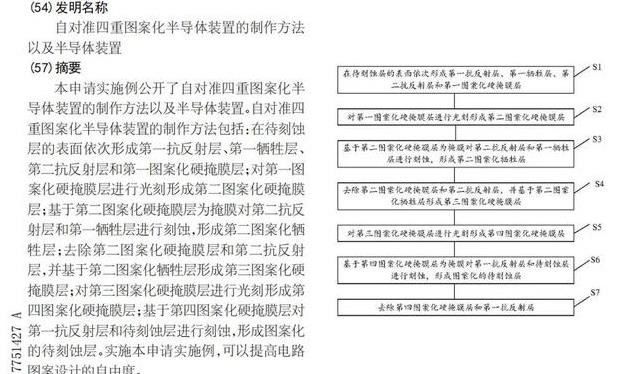

如果来到10nm、7nm等先进工艺节点,需要用到三重图案化工艺,也就是自对准双重图案技术(SADP)。如果继续将工艺下探到5nm节点,在用DUV设备的前提下,必须要用到自对准四重图案化技术(SAQP),这是目前已知的唯一方法。

但是这个方法,台积电没有尝试过,英特尔没有尝试过,三星没有尝试过。因为以上三家,都已经切换到了EUV工艺,不需要再投入大量的资金去攻克技术。

这个未知的技术空间,给到了中国大陆的晶圆企业。

深圳的企业已经申请了自对准四重图案化技术的专利,剩下的,就要看我们的其他国产供应链企业,需要多长时间来解决成本和良品率的问题了。