钼缓冲层对SiC功率器件封装可靠性的影响

刘洋志 卢盛辉 吴丽娟 宋宣廷 李良良

(长沙理工大学南宁职业技术学院)

摘要:

采用有限元分析方法,对有无钼缓冲层的两种封装结构进行了热循环和稳态热机械可靠性对比研究。结果表明,在封装中加入钼缓冲层后对芯片的金属化层的影响较小,但使碳化硅芯片的等效应力降低了60.2%,芯片焊料层的等效应力降低了46.28%,同时芯片焊料层的疲劳寿命增加了约1380倍。进一步用响应面法(RSM)分析了钼缓冲层的尺寸对封装中各组件的应力和应变的影响,结果表明,钼缓冲层的直径接近芯片的对角线长度时,寿命最佳;增加缓冲层厚度可提升缓冲效果,但会降低底座焊料层寿命;钼缓冲层最优厚度为0.5~0.7mm,对应的芯片焊料层寿命为2058771~1867470次循环,底座焊料层寿命为1026~1049次循环,分别为无钼缓冲层结构的2983~2706倍和1.49~1.52倍。在相同热功耗下,芯片焊料层应力和底座焊料层应力仍分别降低83.6%~85.1%和17.2%~15.1%。

近年来,在电力电子行业中,碳化硅功率器件的发展大大提升了半导体器件的性能。自2001年英飞凌公司率先量产碳化硅SBD并进入市场以来,碳化硅功率器件凭借其正向压降低、开关速度快、导热性能好等特点,适用于轨道交通、智能电网等高端领域,且一直有着良好的应用前景。

碳化硅芯片工作时可以维持高的结温,但这会导致更严重的热应力,进而可能使芯片的电气性能恶化[1]。对此问题,合适的封装技术可以提高碳化硅模块的可靠性,国内外研究者们对改进碳化硅封装可靠性展开了研究[2-5]。如在材料方面,Wagner等[6]通过有限元功率循环仿真,比较了分别使用陶瓷化合物封装和高分子聚合物封装对单个碳化硅功率模块的影响,发现随着封装物刚度的增加,模块可靠性和使用寿命随之增加。Bai等[7]通过温度循环试验,探究低温烧结银作为碳化硅芯片连接层时的热疲劳寿命和失效机理,发现其在DBC基板上具有高可靠性。优化封装结构或布局同样是一种提升模块可靠性的方法,如用响应面曲线法和蚁群优化-反向传播神经网络方法,对封装中碳化硅MOSFET芯片的位置进行优化来降低结温和热机械应力[8]。或使用田口试验法优化倒凹槽焊点结构来增加焊点的热疲劳寿命[9]。针对碳化硅器件封装会承受更大热应力的问题,在封装中引入钼缓冲层可以提高模块的可靠性[10-11],然而目前国内外学者对此开展的研究尚存不足,如钼缓冲层多应用在压接型封装中,而对应用于焊接式封装的研究较少,更没有进一步分析钼缓冲层结构参数对温度循环条件下各组件应力应变的影响规律,以及没有在缓冲层结构参数优化方面展开深入研究。

为深入了解钼缓冲层及其尺寸变化对各组件的影响,本文采用有限元分析方法对有无钼缓冲层的焊接式封装结构进行热循环可靠性加速试验仿真,探究了引入钼缓冲层后各组件应力或者应变的变化。接着通过进一步计算得到两种封装的焊料层危险点处的等效塑性应变范围,并用于预测焊料层的疲劳寿命。随后利用响应面曲线方法分析了钼缓冲层的尺寸对封装中各组件应力或应变的影响,并通过仿真进一步研究钼缓冲层的最优尺寸。最后讨论了引入钼缓冲层对热阻以及封装可靠性的影响。本研究将为SiC功率模块封装结构的优化和设计提供参考。

1 有限元模型和材料参数

1.1 有限元模型

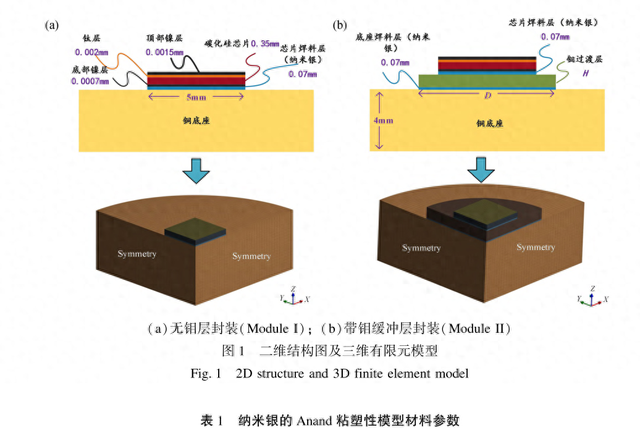

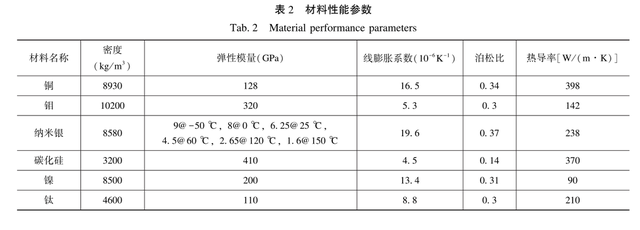

本文以是否带钼缓冲层的焊接式封装作为研究对象,各组件尺寸如图1二维结构所示,其中(a)为无钼层封装,(b)为带钼缓冲层封装。D和H分别是钼缓冲层的直径和厚度,初始取值分别为7.5mm和0.7mm。在有限元工具中对关键结构建立三维有限元模型,考虑到结构对称性,采取四分之一的模型进行计算。将两个侧面设置为对称面,对铜底座的底面施加X、Y、Z方向的零位移约束。仿真中组件的几何参数和材料参数均与实际相同。各个组件材料都是各向同性和线性弹性的,且纳米银焊料同时耦合了粘塑性材料特性。描述纳米银粘塑性行为的Anand模型如表1所示,各组件材料参数如表2所示。

1.2 仿真方法

对两种封装结构进行热循环可靠性加速试验仿真。试验的加载按照JESD22-A104D标准进行。初始零应力温度设置为室温25℃,温度范围从-55℃到+150℃,极端温度下的驻留时间为15min。试验过程中为了避免测试样品的瞬态热梯度对失效的影响,升降温速率不应超过15℃/min,根据这一原则,试验中设定升降温时间均为15min,每个周期持续60min。在热循环过程中,焊料中的应力和应变表现出周期性的变化,并在经历几个周期的加载后稳定下来,因此本文进行四个温度周期的有限元仿真。

2 结果与讨论

2.1 热循环模拟

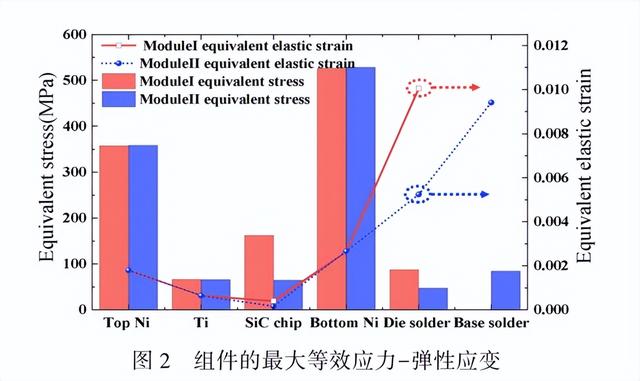

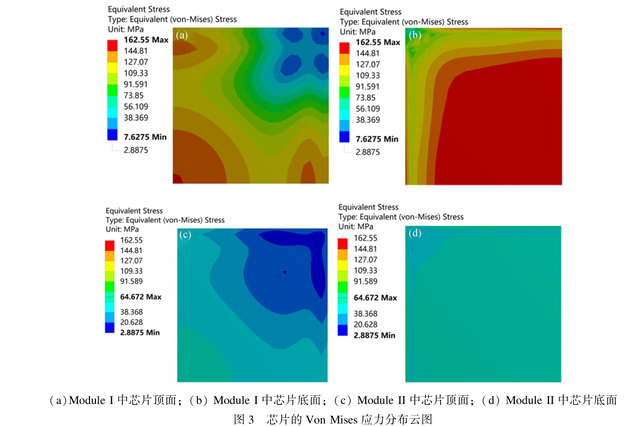

在整个封装结构中,不同的组件具有不同的热膨胀系数,当温度发生改变后将在每个组件上产生热应力,各组件在热循环中的最大应力-弹性应变如图2所示。在两种封装结构中,碳化硅芯片和镍金属层具有较大的弹性模量,热应变较小且受到较大的热应力。纳米银具有较大的热膨胀系数和较低的弹性模量,因此容易产生较大的热应变。对比两种封装,引入钼缓冲层后各组件的应力和应变都得到了不同程度的缓解。芯片最大等效应力(VonMises应力)从162.55MPa减至64.67MPa,降低了60.2%,芯片连接层的最大等效应力从87.48MPa降至46.99MPa,减少了46.28%。而芯片金属化层具有较薄的厚度,其与相邻组件产生的热膨胀体积差异较小,主要受到来自于其他组件传递过来的应力,因此应力变化较小。芯片VonMises应力分布云图如图3所示。焊接式封装的芯片底面由于接近铜底座而出现大面积的应力集中。加入钼缓冲层后,应力分布与ModuleI相似,但应力整体降低。这是由于应力主要来自铜和碳化硅芯片之间热膨胀系数的失配,而钼的热膨胀系数介于铜和碳化硅之间,引入钼缓冲层降低了封装的应力梯度,缓解了组件之间热失配的程度。

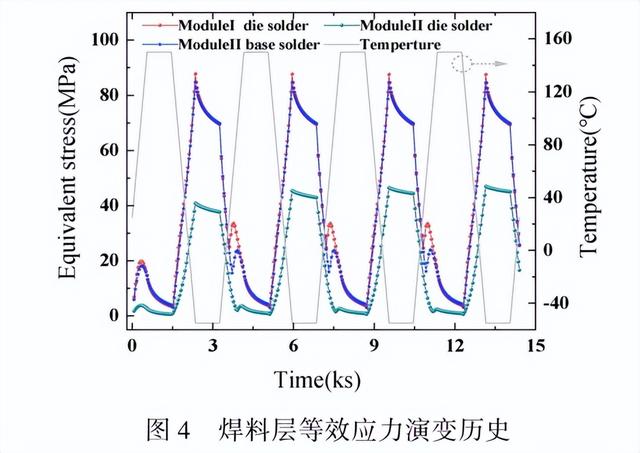

焊料层在温度循环过程中应力随时间变化如图4所示。在应力演变过程中,可以观察到明显的应力松弛现象。25℃为无应力状态,当温度从25℃到150℃时,焊料层和周围组件的膨胀体积差异产生热应力,但热应力很快被应力松弛所补偿,且纳米银的弹性模量随着温度的升高而降低,这产生了一个先增加随后迅速减小的应力恢复峰。在高温驻留时间内,应力松弛占据主导地位,焊料层等效应力持续降低直到温度开始下降,材料由膨胀转为收缩,焊料应力持续升高。当焊料层处于低温驻留时间时,应力松弛继续占据主导地位,应力从高点开始回落。随后在温度从-55℃恢复到室温25℃的升温过程中,应力迅速下降,但最终并没有回到无应力状态,这表明温度卸载后产生了残余应力。

有研究表明焊料层在升温过程中出现的应力恢复峰值受到周围组件热膨胀系数大小的影响,尤其对基底层的热膨胀系数变化较为敏感[13]。随着钼缓冲层的加入,焊料层在温度循环中承受的最大等效应力和应力恢复峰都不同程度地下降,应力演变趋于稳定后ModuleII中芯片焊料层应力恢复峰从ModuleI中的33.47MPa降至2.39MPa,底座焊料层的应力恢复峰值降至23.85MPa。应力恢复峰的大小反应了组件之间热失配的程度,即钼缓冲层的加入使所有焊料层的热失配程度得到改善。

2 结果与讨论

2.2 寿命计算

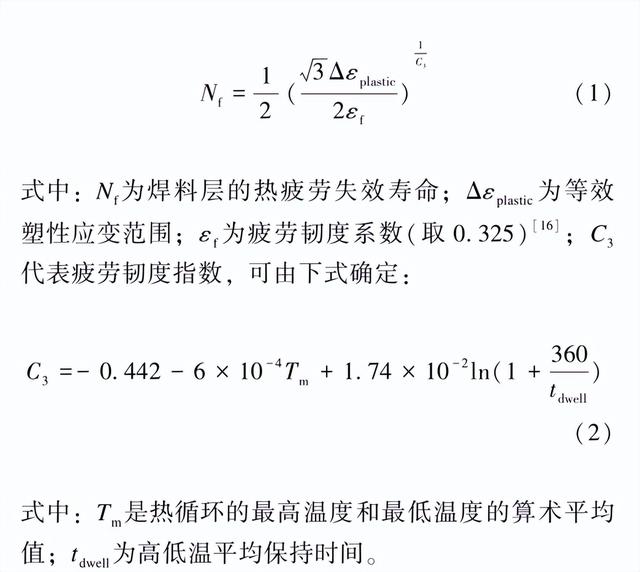

焊料层既是整个结构的重要连接部分,也是结构中最容易失效的组件。Coffin-Manson模型[14]以焊料层出现疲劳裂纹作为失效判据,是一种广泛应用于分析金属或焊接材料在循环塑性变形下寿命的方法。Yang等[15]使用了Engel-Maier的Coffin-Manson修正模型来获得纳米银焊料更准确的寿命预测结果。由热循环仿真结果得到焊料的等效塑性应变范围,其疲劳寿命可采用以下模型进行预测:

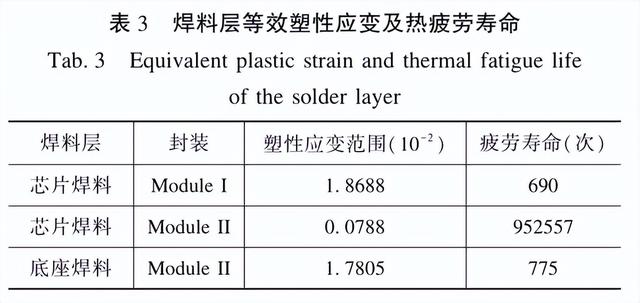

将焊料层的最大塑性应变处定义为危险点,芯片焊料层的最大塑性应变集中在直角边角,底座焊料层的最大塑性应变集中在圆弧外圈。如表3所示,通过计算得到两种封装中焊料层危险点的塑性应变范围,代入公式(1)得到疲劳寿命。计算得到ModuleI中芯片焊料层疲劳寿命为690次循环,ModuleII中芯片焊料层和底座焊料层的疲劳寿命分别为952557次循环和775次循环。

综上,通过在封装中焊接钼缓冲层,能够提高各焊料层疲劳寿命,其中芯片焊料层的疲劳寿命增加约1380倍。但底座焊料层热疲劳寿命与ModuleI中芯片焊料层寿命相比只有少量提升,其原因是:一方面钼的线膨胀系数(5.3×10-6K-1)比碳化硅芯片的线膨胀系数(4.5×10-6K-1)更接近铜底座的线膨胀系数(16.5×10-6K-1),ModuleII中的底座焊料比ModuleI中芯片焊料会具有更好的可靠性;另一方面,钼片的尺寸对焊料层寿命同样会产生影响,钼缓冲层尺寸比芯片更大,这从一定程度上增加了底座焊料的应力和应变,降低了寿命,因此,底座焊料层热疲劳寿命提升不明显。

3 响应面曲线分析

3.1 仿真试验设计

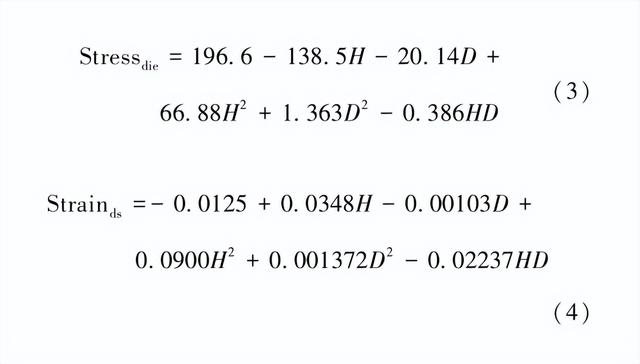

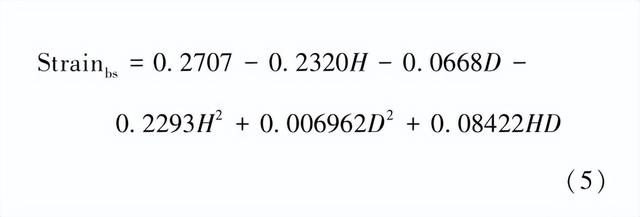

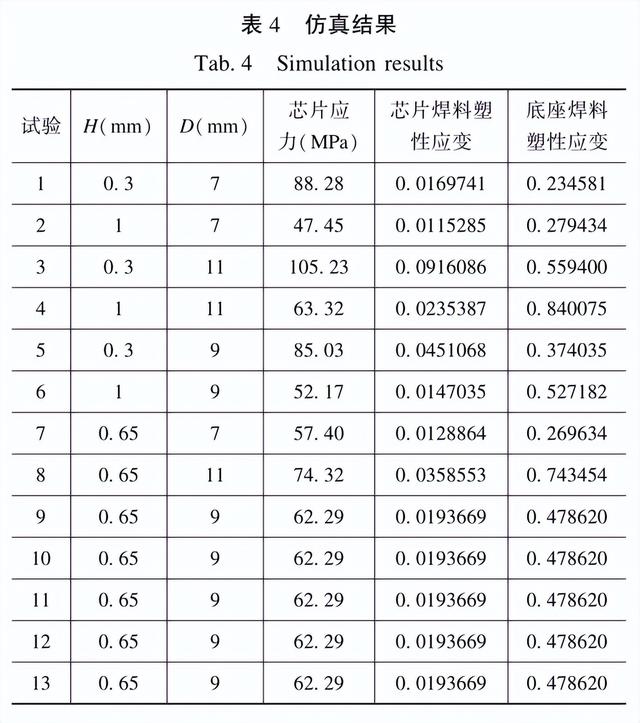

由上文可知,钼缓冲层可有效降低碳化硅芯片的应力,并增加焊料层的热疲劳寿命。为进一步研究钼缓冲层的尺寸对封装中各个组件的影响,以钼缓冲层厚度和直径为参数,取缓冲层厚度为0.3~1mm,直径为7~11mm。利用响应面分析的中心复合试验设计方案设计出组合表,由于焊料层的热损伤积累通常可以用等效塑性应变来描述,所以选择焊料层在经历四次温度循环后累计的塑性应变和芯片等效应力作为分析对象。建立出的相应13组模型以及仿真结果如表4所示,对仿真结果进行二次多项式回归拟合,得到温度循环过程中芯片受到的最大应力以及循环结束后焊料层累计的塑性应变回归模型公式如下:

式中:Stressdie为芯片应力;Strainds为芯片焊料塑性应变;Strainbs为底座焊料塑性应变。为验证上述模型,进行3组验证仿真,模型结果与仿真结果基本一致,误差在10%以内,验证仿真结果如表5所示。

3.2 响应面曲线分析

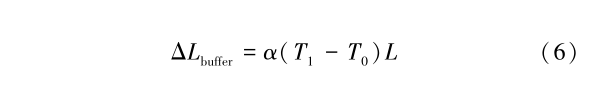

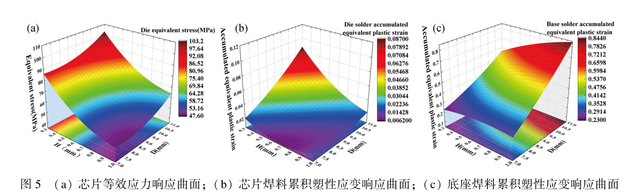

为了进一步分析缓冲层的直径和厚度对芯片和焊料层可靠性的影响,对式(3)、(4)、(5)回归模型进行响应面分析,构建的响应面曲线如图5所示。封装结构中温度改变后缓冲层的自由通胀量如式(6)。

式中:L为缓冲层的初始长度,在垂直方向等于缓冲层厚度H,在水平方向等于缓冲层直径D;ΔLbuffer为缓冲层的自由通胀量;α为钼的线膨胀系数;初始温度为T0,使其均匀受热之后,温度升至T1。如果材料不受约束,则不会产生热应力。封装中各组件受到相同的加热或冷却,由于组件热膨胀系数不同造成自由通胀量不同,组件彼此相互制约从而产生热应力。钼缓冲层厚度或直径的改变使其原本的自由通胀量发生改变,各组件的热应力也随之变化。

由图5可见,随着缓冲层直径的增加,缓冲层和周围组件之间热失配程度加剧,芯片应力和焊料层塑性应变都随之增加。当缓冲层厚度为0.65mm时,随着直径从11mm降低到7mm,芯片应力从74.32MPa降至57.40MPa,芯片焊料层累计塑性应变从0.0358553降至0.0128864,底座焊料层累计塑性应变从0.743454降至0.269634。各焊料层的可靠性随着缓冲层直径的减小而提高。

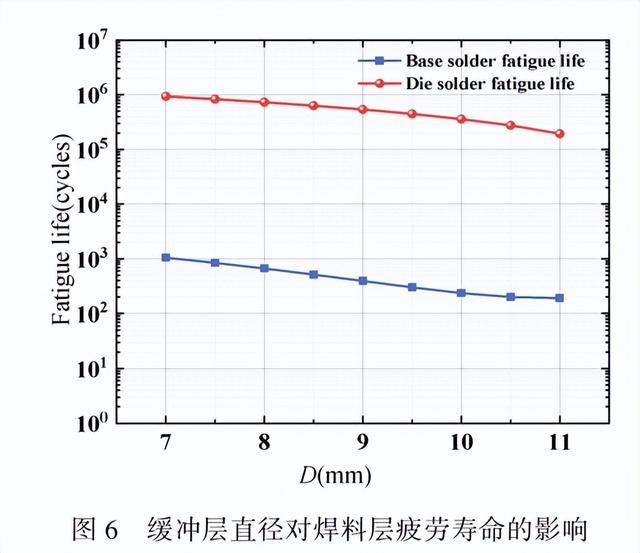

各焊料层疲劳寿命随缓冲层直径变化如图6所示,随着缓冲层直径从11mm降至7mm,芯片焊料层寿命从193681次循环增至933197次循环,底座焊料层从192次循环增至1047次循环。即缓冲层直径接近芯片对角线长度时各焊料层寿命最佳。

同理,随着缓冲层厚度增加,位于缓冲层和铜底座之间的底座焊料层塑性应变也随之增加。当缓冲层直径为7mm时,随着厚度从0.3mm增至1mm,底座焊料层累计塑性应变从0.234581增至0.279434。但缓冲层顶部的芯片焊料层塑性应变和芯片应力却随之降低,芯片应力从88.28MPa降至47.45MPa,芯片焊料层累计塑性应变从0.0169741降至0.0115285。这是由于钼和碳化硅之间的热膨胀系数相差较小,厚度的增加虽然会导致钼和碳化硅之间应力的增加,但在封装中这不是热应力的主要来源,封装的主要热应力-应变源自缓冲层和铜底座界面,而缓冲层厚度增加给其顶部组件提供了更好的缓冲作用。

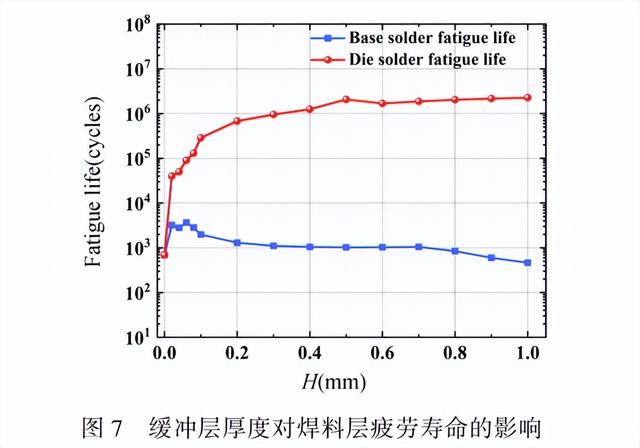

为进一步研究钼缓冲层的最优厚度,取芯片的对角线长度为缓冲层直径,对不同缓冲层厚度的结构进行热循环仿真。焊料层疲劳寿命随缓冲层厚度变化如图7所示,随着缓冲层厚度从0mm增至0.06mm,芯片焊料层与底座焊料层的疲劳寿命从690次循环分别增至89995次与3677次循环,此时底座焊料层达到寿命的峰值。随着厚度继续从0.06mm增至0.8mm,芯片焊料层疲劳寿命达到2034014次循环,而底座焊料层疲劳寿命降至844次循环。

这是由于缓冲层厚度非常薄时,两层焊料层的热应力-应变来自于碳化硅芯片和铜底座之间的热失配,而缓冲层缓解了其热失配程度,芯片焊料层和底座焊料层的寿命都随厚度增加而增大。但随着缓冲层厚度继续增大,缓冲层和铜底座之间的热失配程度开始加剧,并成为底座焊料层热应力的主要来源,底座焊料层寿命随缓冲层厚度增加而降低。碳化硅芯片与缓冲层的热膨胀系数相差较小,同时缓冲层为芯片焊料层缓冲了来自缓冲层和铜底座之间的热失配。因此芯片焊料层的寿命随着厚度增加首先迅速增加,随后趋于平缓。

当缓冲层厚度从0.8mm增至1mm,芯片焊料层疲劳寿命增至2257963次循环。底座焊料层疲劳寿命844次循环降至463次循环,此时其疲劳寿命低于ModuleI芯片焊料层寿命,因此缓冲层的最优厚度为0.5~0.7mm,在这个区间内,各焊料层寿命变化相对平缓。对应的芯片焊料层寿命为2058771~1867470次循环,底座焊料层寿命为1026~1049次循环,分别为无钼缓冲层结构的2983~2706倍和1.49~1.52倍。

4 稳态热机械仿真

结壳热阻是衡量功率器件封装散热能力的重要指标参数,器件的功率容量和热可靠性都与热阻相关。钼缓冲层的引入会改变封装的热阻,为了探究钼缓冲层对热阻以及封装可靠性的影响,对尺寸优化后的带钼缓冲层封装结构进行稳态热机械仿真。仿真中,将散热器的散热作用等效为对流换热作用,其等效对流换热系数为2000W/(m2·℃),环境温度为25℃。稳态工作下,根据结壳热阻定义:

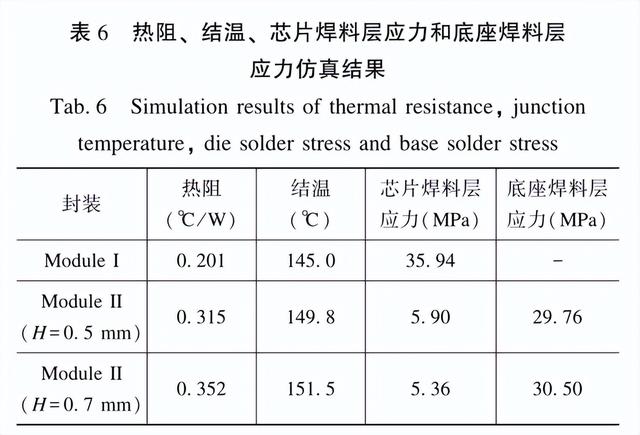

式中:Rth是器件结壳热阻;P是器件耗散功率;Tj为芯片结温度;Tc为底座底部的温度。热阻计算结果如表6所示,得益于纳米银焊料和铜底座良好的热导率,ModuleI的结壳热阻仅为0.201℃/W。钼缓冲层的引入增加了封装的热阻,尺寸优化后ModuleII的结壳热阻分别为0.315℃/W(H=0.5mm)和0.352℃/W(H=0.7mm),同比增加56.7%和75.1%。热阻的增大使封装散热能力下降,进而导致芯片结温升高。在器件44W功耗下,ModuleI和ModuleII的结温和焊料层等效应力如表6所示,其中ModuleI的芯片结温最低,为145.0℃。而钼缓冲层厚度分别取0.5mm和0.7mm时,结温分别较ModuleI增加4.8℃和6.5℃。在本文进行对比的两种封装中,所有材料都具有较大临界温度,如熔化温度和玻璃转换态温度。其中为了应对SiC功率器件的高温运行,纳米银焊料在完成烧结后可以在超过300℃的环境下工作[17-18],远远高于功率器件的典型最高工作温度(150~175℃)和本文的结温结果。

热膨胀引起的热应力-应变是导致器件发生故障的根源。在相同功耗下,ModuleI焊料层最大等效应力为35.94MPa。由于钼缓冲层的引入缓解了组件之间热失配的程度,与ModuleI焊料层应力相比,尺寸优化后ModuleII芯片焊料层应力和底座焊料层应力分别降低83.6%~85.1%和17.2%~15.1%。结果表明钼缓冲层的引入牺牲了一定程度的热阻和结温,但仍降低了焊料层应力,提高了可靠性。

5 结论

本文采用有限元分析方法,通过热循环加速试验仿真分析了两种碳化硅器件封装的热可靠性,以探究钼缓冲层对封装中各组件的影响,结果表明:

(1)钼缓冲层的加入为碳化硅芯片提供了缓冲作用,芯片的等效应力减少了60.2%,芯片焊料层的等效应力减少了46.28%,应力恢复峰从33.47MPa降至2.39MPa,对芯片金属化层的影响较小;

(2)焊料层塑性应变的积累最终会导致其开裂。使用基于塑性应变的Coffin-Manson寿命预测方程,计算得到ModuleI中芯片焊料层的寿命为690次循环,而ModuleII中芯片焊料层和底座焊料层的寿命分别为952557次循环和775次循环。引入钼缓冲层使芯片焊料层疲劳寿命增加了约1380倍,显著提高了封装的可靠性;

(3)缓冲层直径的增加加剧了组件间热失配程度,封装中各组件的热应力-应变随之增加,缓冲层的直径应接近芯片的对角线长度。缓冲层厚度的增加增强了其缓冲作用,芯片和芯片焊料层的热应力-应变得到改善。缓冲层的最优厚度为0.5~0.7mm,芯片焊料层和底座焊料层疲劳寿命分别为无钼缓冲层结构的2983~2706倍和1.49~1.52倍;

(4)通过稳态热机械仿真研究了钼缓冲层对热阻和封装可靠性的影响。尺寸优化后的ModuleII结壳热阻比ModuleI结壳热阻分别增加56.7%(H=0.5mm)和75.1%(H=0.7mm)。在相同热功耗下,ModuleII芯片虽然结温升高,但与ModuleI相比,其焊料层应力和底座焊料层应力分别降低83.6%~85.1%和17.2%~15.1%,具有更高的可靠性。

本研究为进一步优化碳化硅功率模块的封装结构设计提供了参考。