AIP74LVC244 TSSOP20

产品描述SN74LVC244APWR/74LVC244APW/SN74LVC244ADWR/74LVC244AD/AIP74LVC244 是具有三态输出的八路同相缓冲器/线驱动器。三态输出由输出使能输入1OE和2OE控制。nOE上的高电平导致输出呈现高阻态。输入可由 3.3V 或 5.0V 器件驱动。在三态模式中,输出可接 5V。这些功能允许在 3.3V 和 5V 混合环境中将电路用作转换器。

其主要特点如下:

● 与5V逻辑接口的5V耐压输入/输出

● 具有较宽的电源电压范围为:1.2V~3.6V

● CMOS低功耗

● 与TTL电平直接接口

● 输入能通过高达5.5V的电压

● VCC=0V时为高阻抗

● 封装形式:SOP20/TSSOP20/DHVQFN20

应用✔

→ 服务器 ←

→ 发光二极管 (LED) 显示屏 ←

→ 网络交换机 ←

→ 电信基础设施 ←

→ 电机驱动器 ←

→ I/O 扩展器 ←

基础参数类型: 缓冲器,非反相

输入类型: - 输出类型: 三态

工作电压:1.65V~3.6V

工作温度:-40℃~+105℃

静态电流(最大值): 40uA

不同 V,最大 CL 时S的最大传播延迟: 7.5ns@3.3V,50pF

低电平输出电流(IOL): 24mA

高电平输出电流(IOH): 24mA

逻辑电平-高: 1.7V~2V

逻辑电平-低: 0.7V~0.8V

极限参数

交流参数

逻辑符号

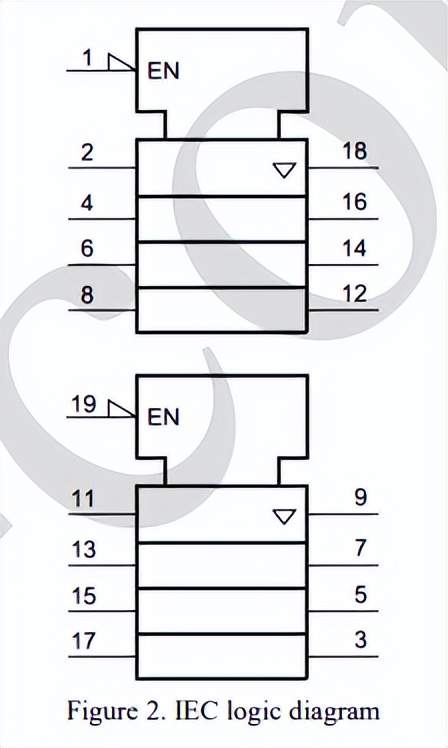

IEC 逻辑符号

功能框图

引脚图及功能

引脚排列图

引脚说明

功能表

应用电路图

本文引用地址:http://www.eepw.com.cn/article/201611/319426.htm

图1-1硬件原理图

硬件原理图很简单了,74LVC244是用来驱动LED的,74LVC244内部就是8个三态门,关于它的详细电气参数,请参阅它的数据手册。关于程序也不是太难,有几个地方要说一下。即然是GPIO实验,当然要关注GPIO的配置了,由于大部分引脚都具有一个以上功能,所以首先要配置引脚功能寄存器PINSEL,只有当引脚配置为GPIO功能时,GPIO的方向位才有效,对于其它功能来说,方向是自动的。关于引脚功能寄存器PINSEL功能如下表所示:

PINSEL0~PINSEL9的值

功能

复位后的值

00

默认功能,通常为GPIO口

00

01

第一个可选功能

10

第二个可选功能

11

第三个可选功能

PINSEL寄存器每两位控制一个引脚,由于各个引脚的功能不一样,所以PINSEL0~PINSEL9的配置也相应的有所不同,想详细了解这10个寄存器的功能可以参看《user.manual.lpc17xx》,这个手册可以到NXP的网站上去下载。由于这次实验只是用到GPIO功能,所以暂时不用管这个寄存器,用它的默认值就可以了。

另一个寄存器是引脚模式选择寄存器PINMODE,它控制所有端口的工作模式,包括是否配置上拉/下拉电阻和特定的开漏操作模式等。引脚模式选择寄存器PINMODE的功能如下表所示:

PINMODE0~PINMODE9的值

功能

复位后的值

00

引脚使能片内上拉电阻

00

01

中断模式

10

引脚没有使能片内上拉/下拉电阻

11

引脚使能下拉电阻

当引脚处于逻辑高电平时,中继模式使能上拉电阻,当引脚处于逻辑低电平时,使能下拉电阻,当引脚配置为输入且不是通过外部驱动时,引脚将保持上一个已知状态。PINMODE_0D寄存器控制寄存器的开漏模式,引脚配置为输出且值为0时,开漏模式会正常地将引脚电平拉低。但是如果输出引脚为1,则引脚输出驱动关闭,等同于改变了引脚的方向,实际上是模拟了一个开漏输出。

PINMODE_0D0~PINMODE_0D4的值

功能

复位后的值

00

引脚处于正常模式(非开漏模式)

00

01

引脚处于开漏模式

除了以上两个寄存器要配置,与GPIO端口相关的寄存器还有快速端口值寄存器FIOPIN可以用来读/写端口的值,端口输出置位寄存器FIOSET,当这个寄存器的相应位置1时,相应端口引脚输出1,当然也可以从这个寄存器读取当前引脚输出的值,与它对应的寄存器是FIOCLR,当寄存器FIOCLR相应位置1时,相应引脚输出0,但这个寄存器是只写寄存器,不能读取数据。好了,关于这些寄存器先总结到这,详细的配置还要看LPC1768的用户手册《user.manual.lpc17xx》,当然也可以经常去NXP网站逛逛看看其它的handbook或whitepaper

好了,下面给出实验程序,由于程序太多,只给出部分,剩下的源文件可以到工程文件夹中去找:

#include"main.h"

volatile unsigned long SysTickCnt;

void SysTick_Handler (void)

{

SysTickCnt++;

}

void DelayMs (unsigned long tick)

{

unsigned long systickcnt;

systickcnt = SysTickCnt;

while ((SysTickCnt - systickcnt) < tick);

}

void PortInit(void)

{

GPIO1->FIODIR = 0xB0000000;

GPIO2->FIODIR = 0x0000007C;

Led1Off();

Led2Off();

Led3Off();

Led4Off();

Led5Off();

Led6Off();

Led7Off();

Led8Off();

}

int main(void)

{

SystemInit();

SysTick_Config(SystemFrequency/1000 - 1);

PortInit();

while(1)

{

Led1On();//LED1开

Led4On();//LED4开

DelayMs(200);

Led1Off();//LED1关

Led4Off();//LED4关

DelayMs(200);

}

}

因为程序是最基础的实验,所以不是太难,程序中延时函数用的是系统节拍定时器,每1m中断一次,系统节拍定时器的中断配置函数是SysTick_Config(uint32_t ticks)它在core_cm3.h中有定义,有兴趣的话可以看看。GPIO是一个结构体指针,原型在LPC17XX.H这个头文件中,其定义的原型如下所示:

typedef struct

{

__IO uint32_t FIODIR;

uint32_t RESERVED0[3];

__IO uint32_t FIOMASK;

__IO uint32_t FIOPIN;

__IO uint32_t FIOSET;

__Ouint32_t FIOCLR;

} GPIO_TypeDef;

还有几个宏定义,如下所示:

1)、#define GPIO1((GPIO_TypeDef *)GPIO1_BASE)

上面这个宏是把GPIO1指向芯片GPIO1的基址上,

2)、#define GPIO1_BASE(GPIO_BASE + 0x00020)

3)、#define GPIO_BASE(0x2009C000UL)

这三个宏就把GPIO的基址定义了出来,关于LPC1768内部地址的分配情况,可以参看它的数据手册,也可参考一下《ARMCortex-M3权威指南》,这本书在网上有电子书,好像宋岩宁牛人早已把它翻译成中文了,懒猫现在也正在参考这本书,另外一定要多去NXP网站看一下它的handbook,whitepaper等资料,还可多到论坛转转,有些坛子里深藏了好多老鸟,好多大虾,好多大牛,有你学的,有你问的,只要肯用心,一根网线,能解决很多问题