背面减薄工艺对 In P 芯片成品率的影响

张圆圆,莫才平,黄晓峰,赵文伯,樊鹏,刘 勋

( 中国电子科技集团公司第四十四研究所)

摘要:

半导体晶圆背面减薄工艺包含临时键合、研磨、解键合、薄片清洗 4 个步骤。 工艺应力损伤使芯片性能劣化甚至失效,成为大光敏区型 InP 基探测器芯片的工艺瓶颈,须加以解决。 将 4个主要步骤分别优化,通过降低键合压力、减少研磨损伤层、保护胶隔绝污染、剥离保护胶摈弃刷洗,使芯片成品率从 30%提高到 95%以上(芯片尺寸 准1000 μm)。 经过多批次流片验证了此方法的正确性和稳定性,对阵列型芯片研制的成品率意义重大,对企业节省生产成本有积极影响。

近年来,计算机、通讯、航空航天工业和其它消费类产品对微电子封装提出了更高的小型化需求,晶圆需减薄至 100 μm 以下,制作成超薄芯片[1](芯片厚度小于 100 μm)。

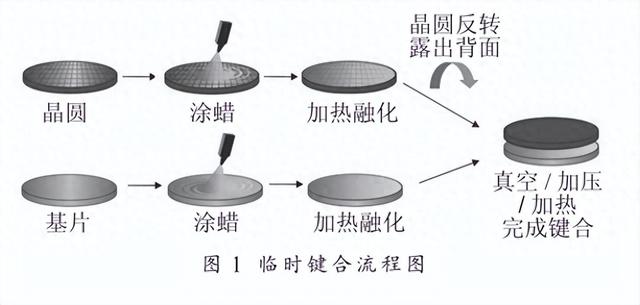

在半导体芯片制造工艺中,芯片首先被制作在晶圆正面,由于后续需要进行背面电极和解理等工艺,以及为提高芯片散热性能等原因,会将晶圆背面的衬底祛除一部分,该工艺过程称为背面减薄 (Back-thinning)。背面减薄工艺包含临时键合、研磨、解键合、清洗 4 个步骤。

1 材料 背 景

InP 是由 III 族元素铟和 V 族元素磷组成的化合物半导体,硬度低,脆性大,易解理[2]。经过单晶生长后切割为半导体标准晶圆。在 InP 晶圆表面可制作探测器和激光器等光电子芯片,在光通信和光电子领域中具有广泛的应用。InP 芯片属于表面器件,被制作在晶圆正面距离表面约 15 μm 的外延层内,外延层是实现“光 - 电”、“电 - 光”转换的核心功能区,微观结构复杂、脆弱易坏。芯片内部的晶体缺陷如晶格位错或点缺陷都将直接导致芯片性能劣化甚至失效报废。本身就具有损伤性的背面减薄工艺极易损伤晶圆,这对芯片的保护提出了很高的工艺挑战。

超薄晶圆具有柔性、易碎性、易翘曲等特点,对晶圆的总厚度变化(TTV)、平整度(TIR)、翘曲度(Warp)有较高的要求[3]。为防止碎裂,会先用中间介质将晶圆临时键合到较厚的载体基片上为其提供结构支撑,露出晶圆的背面待完成减薄或其他背面工艺之后再将其分开,该过程称为临时键合[4,5]- 解键合 (TemporaryBondingand De-bond-ing),如图 1 所示。目前,临时键合工艺常使用固态蜡方式,即通过加热融蜡后施加外力使晶圆与基片键合在一起的方式完成。该方式临时键合并减薄后的薄晶圆翘曲度也是多种方式中最大的 [6],因其应力较大。加压带来的损伤具体表现为:(1)芯片与基片相互物理挤压、摩擦损伤晶体造成缺陷;(2)为 获得 较 小的 蜡 层 TTV,通 常会 施 加相 当 大的外力使键合层薄而平整;(3)蜡层加热冷却的热循环过程中晶圆会产生内应力[7],使得晶圆膨胀 /收缩并产生应力。

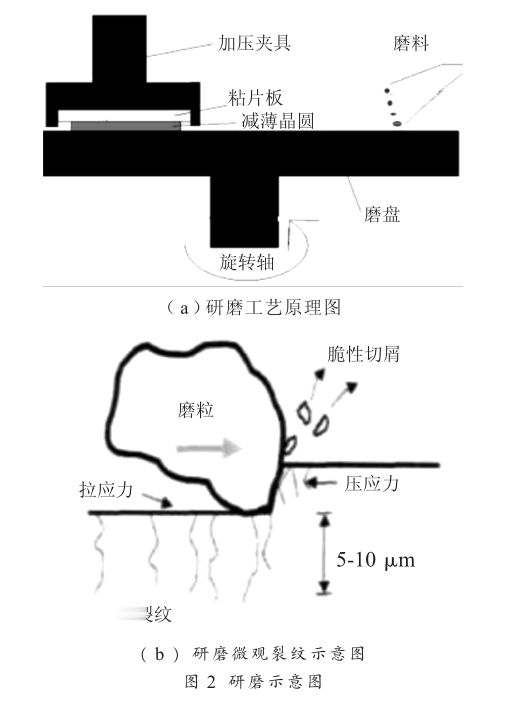

临时键合完成后,通过磨盘研磨方式祛除厚度,如图 2(a)所示。InP 是脆性材料,抗拉应力远大于抗剪应力,其力学性能趋向于脆性,易解理(断裂能仅为 0.63 J/m2)[8],易断裂;另外 ,磷 化 铟InP (克 氏 硬 度 537) 比 常 见 的 硅 Si (克 氏 硬 度1150)材料硬度小,在厚度被减薄后断裂强度就越小,越容易因断裂造成晶圆碎裂报废;背面减薄造成晶体缺陷和微裂纹贯穿延伸至正面影响芯片性能甚至报废,如图 2(b)所示。在工艺中应特别注重对芯片的保护,防止机械应力过大对芯片造成损伤。

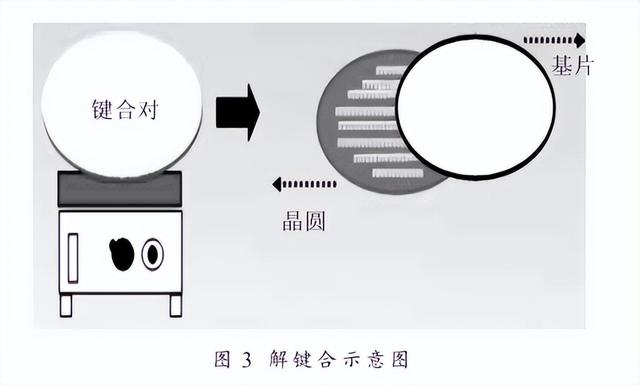

当晶圆被研磨到规定厚度时,将晶圆与基片键合对同时放入去蜡机中浸泡,用电炉加热去蜡液融解蜡层,薄晶圆从基片脱离成为独立的芯片晶圆,如图 3 所示。这种方式属于人工操作,对超薄晶圆的夹持和取拿都会造成一定损伤甚至破碎的风险。

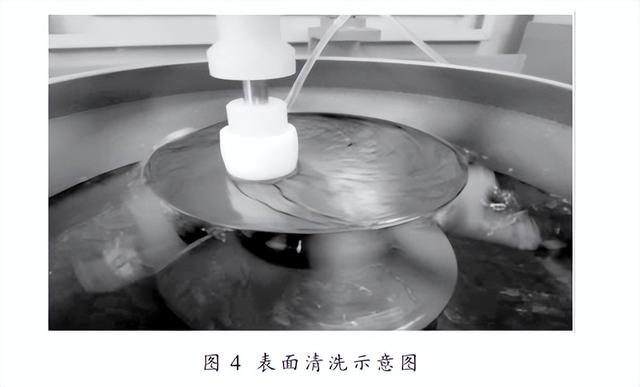

解键合后,需要清洗晶圆表面的键合蜡质。此时蜡质中会混入研磨留下的碎屑颗粒,通常采用有机溶剂冲洗和尼龙微细毛刷刷洗的清洗方式。刷洗过程中毛刷半接触或全接触芯片表面,特别是污渍颗粒(如图 4 所示),会对软质金属凸点造成划伤,破坏芯片结构引起成品率降低。

2 问题 的 提出

近年来,光电子芯片有向大面积、高密度阵列、高台面、高脊型发展的技术趋势,背面减薄工艺中各步骤应力对芯片性能的负面影响逐渐暴露,特别是随着探测器光敏区尺寸变大,芯片成品率显著降低,背面减薄工艺成为该类型芯片的生产瓶颈。

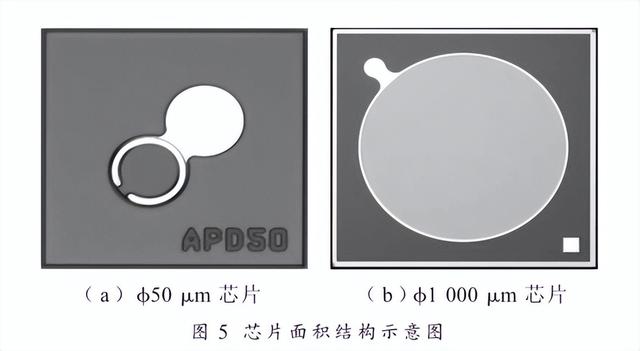

将 小 面 积 芯 片 (准50 μm) 和 大 面 积 芯 片(准1000 μm) 按纵横阵列制作在 InP 晶圆上,各1/2 晶圆。如图 5 所示,每一个方框代表一个芯片单元,方框内的圆形区域即为光敏区。经过测试,成品率均接近 99%。

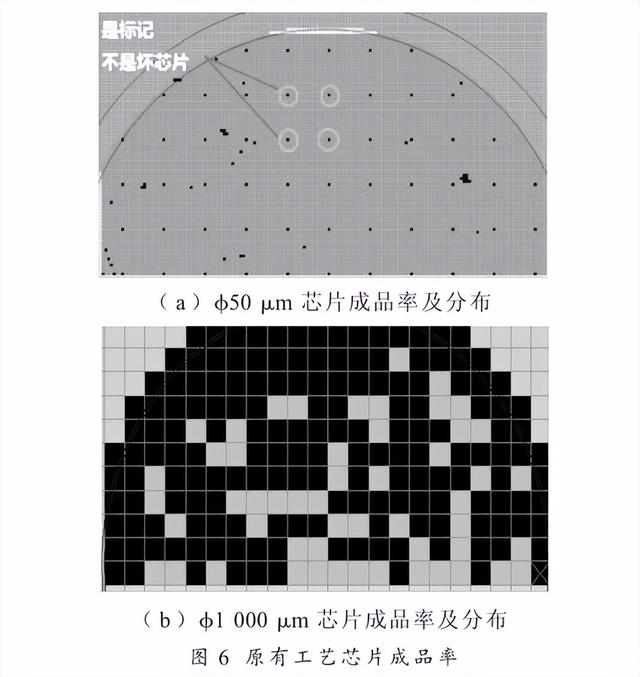

对两个晶圆同时进行背面减薄工艺,测试结果如图 6 所示。在 1/2 晶圆(半圆)中,浅色单元为合格芯片,深色单元为失效芯片。

图 6 可知,准1000 μm 与 准50 μm 芯片晶圆使用 相同 工 艺 进行 背 面 减 薄 后 芯 片 成 品 率 差 别 巨大。准50 μm 成品率达到 99%[图 6(a)]中间距均匀的深色单元是标记,而非失效单元],准1000 μm成品率则不足 30%[如图 6(b)]。确定背面减薄是破坏大面积芯片成品率的关键。

目前的文献资料中对背面减薄的工艺机理、翘曲、清洗方面讨论较多,对芯片的性能影响讨论偏少,本文以光敏区为 准1000 μm 的 InP 探测器芯片为例,阐述背面减薄应力对芯片成品率的破坏程度和坏像元分布,提出解决和优化的方案。

3 试 验 过程

3.1 试 验 准 备

设备 :气 囊加 压 式 临 时 键 合 机(Bonding)、研磨式减薄机(Lapping);

仪器:光电探针测试台;

样品:50 mm InP 芯片晶圆 1/2 片(半圆);

耗材:固态高纯蜡。

依次优化背面减薄中 4 个步骤并分析原因,逐步提高大面积芯片(参考 准1000 μm 型)成品率。

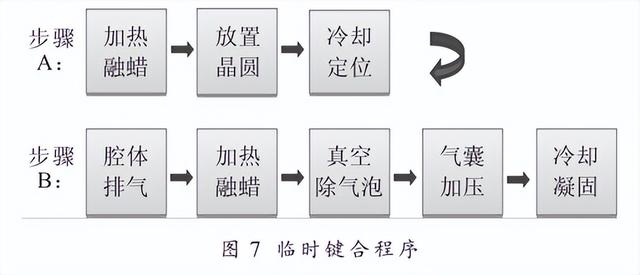

3.2 临时 键 合

由于减薄工艺对总厚度变化(TTV)要 求 高 ,所以临时键合首要考虑蜡层 TTV。临时键合除了要具有优异的粘接性能来抵抗晶圆减薄过程中的机械应力之外,键合层的厚度还必须在整个晶圆范围内具有高度的均匀性,即在经过所有工艺步骤后,整个晶圆范围内要有一个较低的 TTV 。固态蜡临时键合机使用加温、加压、抽真空的方式强行 将 蜡 层 压 薄 、 压 平 、 抽排 气泡 ,以 保 证 蜡 层TTV。分为两个步骤,先进行步骤 A,后进行步骤B,完成临时键合,如图 7 所示。

石蜡高温下融化成液体黏稠度下降,晶圆与基片之间缺少缓冲,当真空腔体中的气囊充气时,气囊对晶圆产生瞬间冲击力和持续压力,造成芯片与基片之间硬接触或碰撞。

冲击应力对 准1000 μm 芯片成品率的破坏主要来源于三方面:

(1)InP 材料易碎易解理,接触式的物理冲击使晶格出现点缺陷、线缺陷;

(2)InP 表面芯片制作完成后,表面缺陷意味着芯片失效;

(3)大面积芯片光敏区内的任何一点出现损伤,便会造成整只芯片失效;小面积芯片光敏区占整个芯片面积的比例较小,随机的损伤点落在光敏区的几率就更低。这也是常规粘片程序加工小芯片时损伤被掩盖的原因。

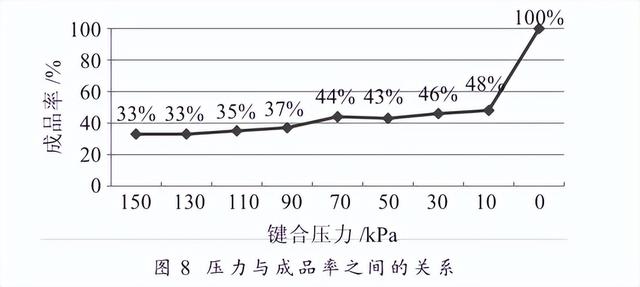

气囊压力对成品率的影响趋势如图 8 所示。随着压力的降低,成品率逐步升高。当压力降为“0”时,晶圆与基片之间的压力只有晶圆自重,两者之间仅有蜡层,并无其他外力致使损伤,成品率为 100%。可见压力是影响成品率最主要的因素,这也应证了原因分析。

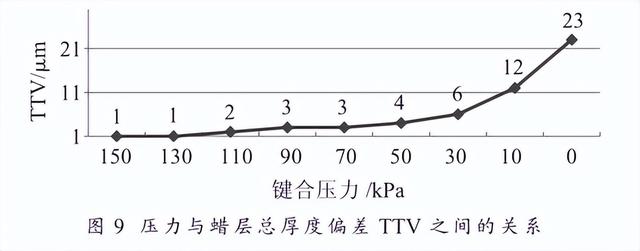

随着晶圆与基片之间压力减小,蜡层 TTV 逐渐劣化,如图 9 所示。当压力降低到 10 kPa 时,TTV 从 1 μm 上 升 到 12 μm 以 上 , 当 压 力 降 为“0”时,晶圆与基片之间的压力只有晶圆自重,没有外力使蜡层变得平整,造成 TTV 剧烈上升到23 μm 的结果。这将直接导致下一步减薄工艺后的晶 圆 厚 度 不 均 匀 。 通 常 , 临 时 键 合工 艺 要 求TTV≤5 μm。

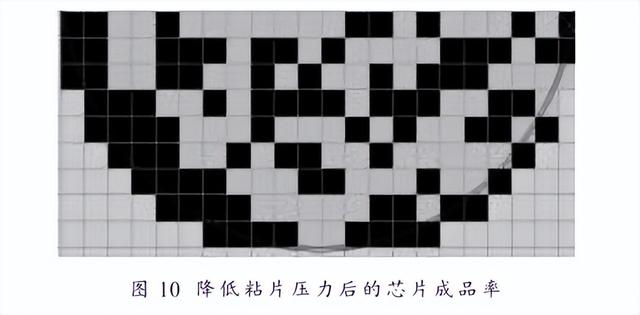

受 TTV 制约,降低临时键合的粘接压力,可以将成品率提高约 10%,达到 45%。如图 10 所示。

3.3 研磨

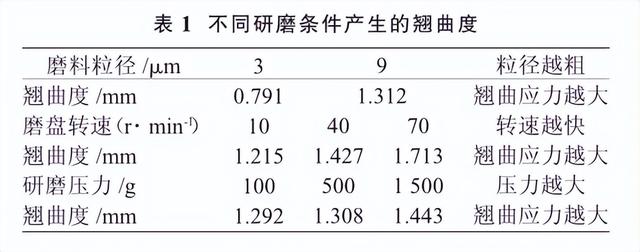

背面减薄属于机械研磨,背面磨损伤形成的碎裂层和形变层会延晶相方向延伸至正面,最终破坏芯片的晶格完整,影响正常功能。经不同工艺参量研磨后的晶圆应力导致的翘曲是不同的,对晶圆的损伤程度也是不同的。试验采用粒径分别为 9 μm 和 3 μm 的磨料以及降低压力、降低磨盘转速三方面进行背面研磨,对比晶圆翘曲度和成品率的差别,如表 1 所示。

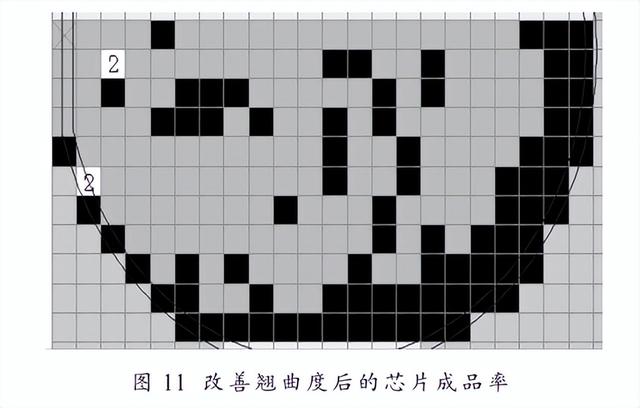

晶圆翘曲应力越大,损伤层越深,对成品率破坏较为明显。虽然可以通过减小工艺参量来控制损伤层,但同时会大幅降低祛除率影响工艺效率。将 工 艺 效 率 和产 品 质 量折 中 考 虑 后 确 定工 艺条件 , 使 准1000 μm 芯 片 成 品 率 从 45% 提高 到75%,如图 11 所示。

3.4 解 键 合

解键合采用浸泡去蜡液的方式,加热溶解蜡层使晶圆与基片分离。虽然晶圆全程浸泡在去蜡液体中,无其他接触性应力产生,对晶圆成品率的破坏非常有限,但是蜡层溶解的过程会造成微量蜡质凝附以及残留去蜡液与研磨碎屑混合物的问题,对下一步表面清洗留下隐患,所以,需要改进解键合的温度与时间,为表面清洗做好工艺准备。为防止晶圆受到污染,试验采用预先涂胶保护的办法,在临时键合之前用光刻胶涂胶一层,作为蜡质与晶圆的阻隔层。此方法不仅大幅减少蜡质与研磨碎屑直接在晶圆上的堆积和污染,并且缩短加热融蜡解键合的时间,去掉用镊子外力推、撬等操作动作,使解键合过程实现自动脱落。最终避免因污染和操作损伤造成的芯片成品率下降的问题。

3.5 薄 片 清洗

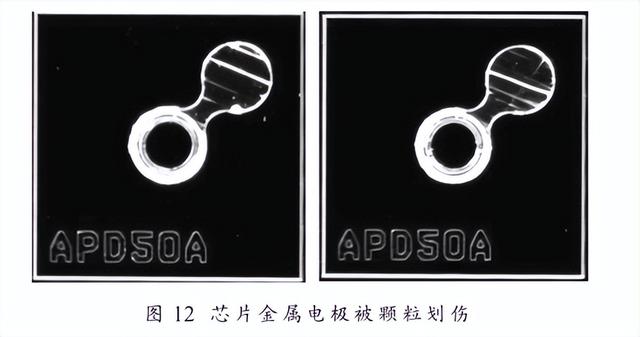

经过涂胶隔绝之后的表面,通过解键合之后先进行有机溶剂去胶清洗,裸露出晶圆表面,再进行表面清洗。表面清洗的损伤主要表现在尼龙软毛刷洗过程中颗粒污染以及颗粒对金属电极的划伤,一旦破坏金属电极的完整性,会造成 PN 结击穿或暗电流增大等劣化结果。这类损伤也会造成芯片成品率的降低,如图 12 所示。

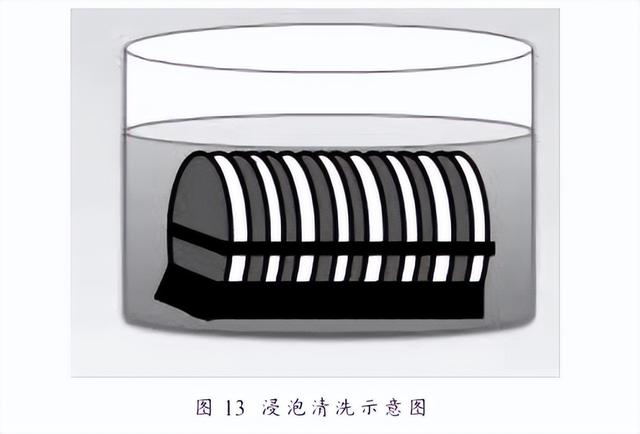

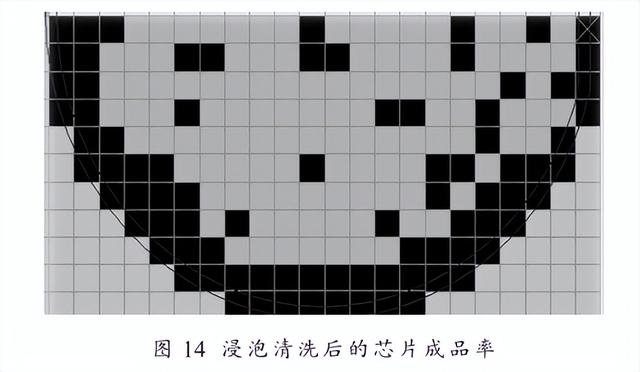

试验在涂有光刻胶的表面进行清洗,通过有机溶剂浸泡,高温有机溶剂冲洗的方式剥离掉保护胶层的污染物,摈弃物理性刷洗,使其在不产生电极划痕的同时确保表面洁净度满足工艺要求,如图 13 所示。

成功使成品率从 75%提高到 85%水平,如图14 所示。

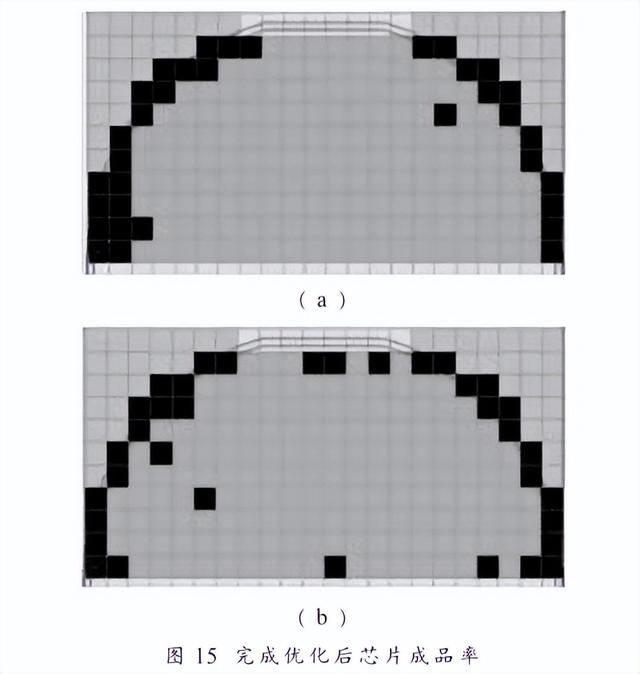

经过多批次生产流片(约 100 片晶圆),论证了该工艺的可行性和稳定性,并未发生成品率高低反复的情况。

在后续工艺过程中,随着工艺优化摸索的深入和熟练,成品率逐渐升高,除去晶圆圆周的不完整芯片以外,晶圆内部芯片几乎达到 99%(如图15 所示),但是坏像元的分布随机。大面积芯片成品率获得与小面积芯片成品率一样的水平。

将此工艺方式推广到其他大面积芯片,例如面积更大的 准2000 μm、准5000 μm 芯片,均取得稳定且较高的成品率。特别对降低阵列芯片的盲元率有较突出作用。

4 结论

InP 基红外探测器大面积光敏区芯片成品率的优劣与背面减薄工艺有直接关系。以目前的实验结果可知,改善原有工艺中各步骤的应力影响,减轻芯片的应力损伤,可以显著提高成品率。通过长期的量产证明该方式的正确性和稳定性。同时,新的工艺方式指明了提高大面积、大阵列型芯片成品率的背面减薄工艺的研发方向,为提高相关芯片研制成功率有至关重要的作用。另外,在这项工作中进一步拓展了背面减薄相关设备的使用潜力和工艺范围,对各设备的优化改造和换代升级具有重要意义。特别是“0”压力自重式临时键合的工艺设备是可以同时解决临时键合 TTV 和提高芯片成品率的发展方向。