1、模拟信号是如何变成一个数字信号的?

我们把一个放大电路的放大量提高,输入是正弦波,输出原来也是个正弦波。

我们把放大量调大,大到正弦波的幅度足够大,正弦波的波峰和波谷被“削波”,我们发现输出的波形从一个模拟信号,变得像一个数字信号。

我们把示波器调整一下时间轴,看着更像。

我们发现放大量足够大的时候,仿佛输入信号大于某个值Vx的时候,输出高电平,小于这个值Vx的时候,输出低电平。像极了数字电路中,电平标准中VT的定义。

削波失真(clipping distortion)的现象:在放大量提高到一定程度时,输入的正弦波信号会超过放大器的线性工作范围,导致输出信号的波峰和波谷被“削去”。这时候,输出信号的波形看起来像一个方波或脉冲信号,类似于数字信号的高低电平。

在这种情况下,放大器相当于一个比较器,当输入信号超过某个阈值(例如你提到的Vx)时,输出为高电平;当输入信号低于这个阈值时,输出为低电平。这与数字电路中的阈值电压VT类似,表现出数字信号的特性。

在数字电路中,VT(阈值电压)是指逻辑门将输入信号识别为高电平(逻辑1)或低电平(逻辑0)的电压阈值。具体来说:

高电平(逻辑1):输入电压高于阈值电压(VT)时,逻辑门将该信号识别为高电平。

低电平(逻辑0):输入电压低于阈值电压(VT)时,逻辑门将该信号识别为低电平。

不同类型的逻辑门(如CMOS、TTL等)有不同的阈值电压,但基本原理相同。阈值电压是逻辑电路设计中一个关键参数,确保电路能够可靠地识别和处理数字信号。

在数字电路中,亚稳态(metastability)是指在某些条件下,电路不能迅速且可靠地确定输出状态的情况。亚稳态通常发生在时序电路中,尤其是在异步信号交互或时钟边沿较近的情况下。以下是关于亚稳态的详细解释:

原因亚稳态主要发生在触发器(如D触发器)或锁存器中,当输入信号在时钟上升沿或下降沿附近发生变化时,电路可能无法及时做出明确的高低电平判断,进入一种不稳定的中间状态。

表现当电路进入亚稳态时,输出信号可能会在一定时间内保持在一个不确定的电压范围内,而不是明确的高电平或低电平。这种不确定性可能会传递到后续的逻辑电路,导致系统错误。

解决方案同步设计:尽量在同一个时钟域内设计电路,减少异步信号的交互。

多级同步器:使用多级触发器将异步信号同步到系统时钟,以减少亚稳态的概率。

提高时钟频率或设置更长的时序裕量:确保信号有足够的时间稳定在时钟边沿前后。

结合VT和亚稳态的解释在数字电路中,阈值电压(VT)和亚稳态有着密切的关系。当输入信号在VT附近变化且时序条件不满足时,电路容易进入亚稳态。这种情况下,电路不能确定输入信号是否已经跨越了阈值电压,从而导致输出信号不稳定。因此,设计可靠的数字电路时,不仅要考虑阈值电压的设置,还需要关注时序约束和信号同步问题,以减少亚稳态发生的概率。

总之,阈值电压是决定数字电路输入信号识别的重要参数,而亚稳态则是数字电路在某些条件下无法迅速确定输出状态的现象。通过合理设计,可以在确保电路可靠性的同时,减少亚稳态的发生。

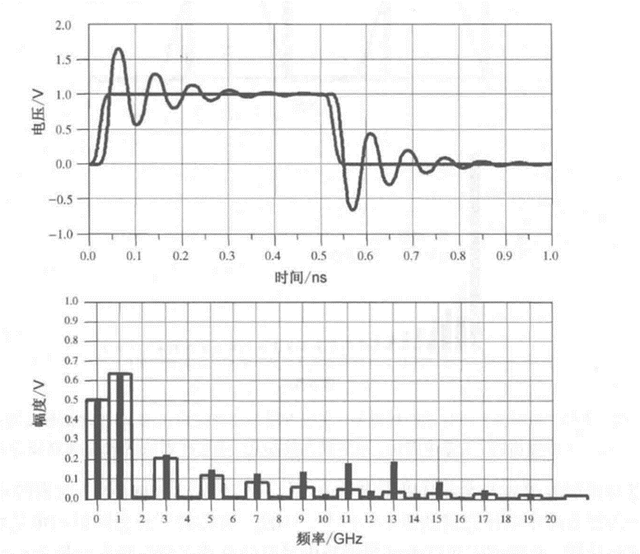

这种现象可以用示波器来观察,当你调整时间轴时,可以更清楚地看到输出信号的方波形态,进一步验证了你的观察。这种模拟信号转变为数字信号的过程在某些应用中是有用的,例如信号处理和数据转换。

总结起来,放大量足够大时,放大器输出信号的削波现象使得它具备了类似于数字电路的特性,将输入的模拟信号转换为具有高低电平的数字信号。

2、一个典型应用——比较器

比较器是一种用于比较两个电压信号的模拟电路,它的输出只有两种状态:高电平或低电平,因此输出结果实际上是一种数字信号。这种特性使得比较器在许多应用中起到了模拟到数字转换的作用。下面详细解释比较器的原理及其本质。

比较器的基本原理比较器有两个输入端:正输入端(V_in+)和负输入端(V_in-)。其输出取决于这两个输入电压的比较结果:

当 V_in+ > V_in- 时,输出为高电平。

当 V_in+ < V_in- 时,输出为低电平。

比较器的内部结构与运算放大器(Operational Amplifier, Op-Amp)类似,但有一些关键的不同点。比较器通常没有反馈网络,因此它的增益非常高,理论上接近无穷大。

理想比较器比较器是一个开环或正反馈的理想运放。无论输入电压大小多少,均被放大到电源电压。其参数特点如下: