半导体技术的进步正逐渐接近极限,延续摩尔定律的步伐放缓。为了突破传统封装技术中I/O引出端数量的限制,扇出型晶圆级封装采用晶圆重构的方法,利用多层再布线(RDL)等技术,减小了引脚间距,降低了封装厚度,减少了高频信号传输损失,进一步提高了芯片的集成度。近年来,这种先进封装技术在消费电子和高性能计算领域迅速发展,并逐渐成为代表性技术。然而,扇出型晶圆级封装(FOWLP)由于结构精密和工艺复杂,其可靠性问题日益显著,涉及到晶圆翘曲、凸点开裂、芯片偏移等系列问题。

01

扇出型封装(FOWLP/FOPLP)

随着先进纳米制程已逼近物理极限,在日益增长性能需求与摩尔定律逐渐失效的矛盾影响下,Intel、NVIDIA、TSMC、AMD等老牌半导体企业纷纷加大对叠层封装(PoP)、FOWLP、硅通孔(TSV)等先进封装领域的投入,要借助先进的封装技术实现更高性能、更低耗电量、更小体积、信号传输速度更快的产品。

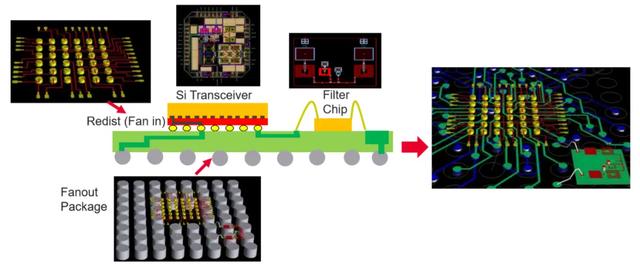

作为先进封装技术的重要成果之一,FOWLP在移动设备和可穿戴设备中取得了巨大成功,并开始在高性能计算、自动驾驶和物联网等领域得到应用。FOWLP具有将多种封装技术相结合的潜力,可以实现异质集成和3D堆叠,为未来封装技术的发展奠定基础。已有多个商用产品采用了FOWLP技术,其中包括FPGA、CPU和DSP等关键元器件,这些技术的应用使它们实现更高密度、高性能和高可靠。

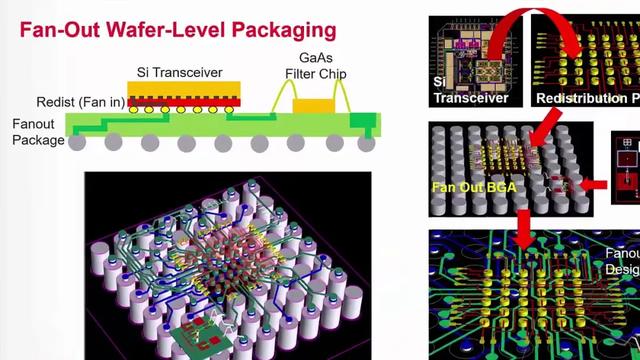

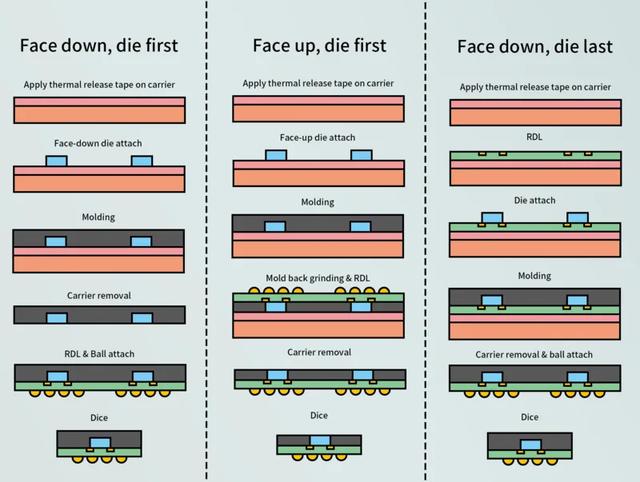

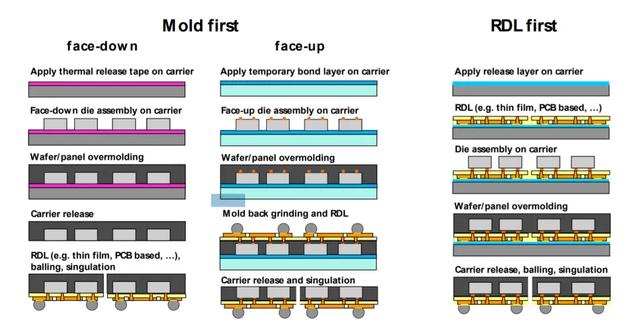

传统封装技术,如倒装封装和引线键合,通常采用引线、通孔和锡球等复杂的互连结构来实现信号的互连。然而,这些复杂的互连结构可能会影响芯片信号传输的性能。在扇出型封装中,根据重布线的工序顺序,可分为先芯片(Chip first)和后芯片(Chip last)两种工艺;根据芯片的放置方式,又可分为面朝上(Face up)和面朝下(Face down)两种工艺。综合上述分类,封装厂根据操作的便利性,形成了三种主要的组合工艺,即面朝上的先芯片处理(Chip first-face up)、面朝下的先芯片处理(Chip first-face down)和面朝下的后芯片处理(Chip last-face down)。

在先进芯片处理工艺中,面朝上的芯片处理由于需要利用化学机械抛光(CMP)技术将塑封层减薄,因此成本较高,一般较少被封装厂采用。相反,面朝下的芯片处理在移除载板并添加重布线层(RDL)制程时,容易引起翘曲现象,因此需要在工艺操作中采取预防措施。面朝下后芯片处理工艺首先采用RDL技术,这样可以降低芯片封装过程中的不合格率,当前在封装厂中也有较多应用。

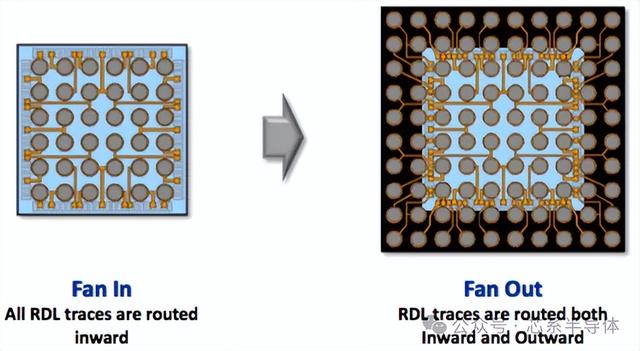

在扇出型晶圆级封装(FOWLP)工艺中,重布线层是关键步骤之一。其在晶圆表面通过沉积金属层和绝缘层形成相应的金属布线图案,利用高分子薄膜材料和铝/铜金属化布线,将芯片的I/O焊盘重新布局为面阵分布形式,并将其延伸到更宽松的区域以便植锡球。扇出型晶圆级封装中主要有两种RDL工艺,分别是:

聚合物+电镀铜+蚀刻PECVD+Cu-damascene+CMP02

可靠性的挑战与思考

半导体技术的进步正逐渐接近极限,延续摩尔定律的步伐放缓。为了突破传统封装技术中I/O引出端数量的限制,扇出型晶圆级封装采用晶圆重构的方法。这种技术利用多层再布线(RDL)等技术,减小了引脚间距,降低了封装厚度,减少了高频信号传输损失,进一步提高了芯片的集成度。近年来,这种先进封装技术在消费电子和高性能计算领域迅速发展,并逐渐成为代表性技术。然而,扇出型晶圆级封装(FOWLP)由于结构精密和复杂的生产流程,其可靠性问题日益显著。

随着先进纳米制程已逼近物理极限,在日益增长的性能需求与摩尔定律逐渐失效的矛盾影响下,Intel、NVIDIA、TSMC、AMD等老牌半导体企业纷纷加大了对叠层封装(PoP)、FOWLP、硅通孔(TSV)等先进封装领域的投入,要借助先进的封装技术实现更高性能、更低耗电量、更小体积、信号传输速度更快的产品。

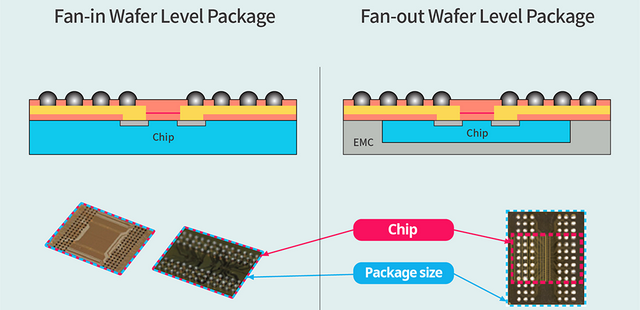

FOWLP中有两个重要概念:扇出型封装和晶圆级封装。传统的扇入型封装将I/O接口放在晶片下方,受限于芯片尺寸,I/O数量受限。扇出型封装利用重布线技术和模塑化合物,在晶片外部提供额外芯片面积,增加了I/O接口数量,满足了芯片不断增长的吞吐需求。晶圆级封装则是先对整个晶圆进行封装,然后再进行切割,更适合大规模集成电路的批量生产。

随着集成电路封装技术的进步,封装结构变得更加复杂,布线密度和I/O接口数量不断增加。这种复杂性导致了可靠性问题的增加,尤其是在FOWLP工艺中。FOWLP工艺包括多个步骤,如晶圆重构、塑封和重布线,每一步都对封装的可靠性产生重要影响。

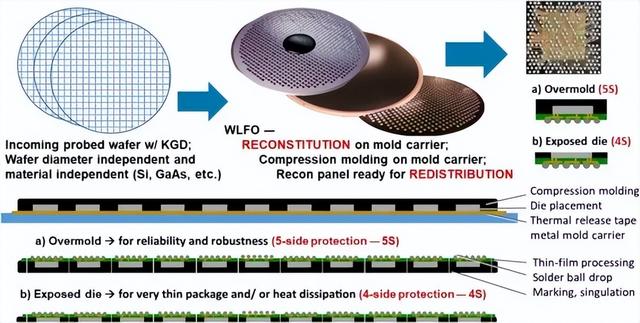

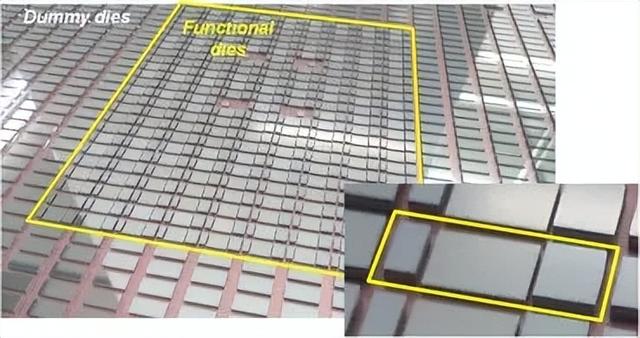

晶圆重构是将晶圆上分离下来的芯片重新组装到临时载体上,形成新的“重构晶圆”,如下图所示。晶圆重构技术要求较好的定位精度,既需要良好的粘贴强度,也需要易于剥离,否则会导致芯片偏移。

环氧塑封工艺可保护芯片并扩展其表面积。然而,环氧塑封料在受热后会液化。不匹配热膨胀系数可能导致晶圆翘曲和芯片偏移,而注塑时液体流动也可能改变晶粒位置。重布线技术是实现扇出效果的关键,该技术首先在晶粒表面覆盖钝化层和PI层,然后通过金属溅射和掩膜曝光制造金属层图案,使用电镀法填充金属层,并在晶粒和塑封料表面交替制作金属层和聚酰亚胺层,最终形成多层重布线层以重新排布I/O接口。然而,由于金属和聚酰亚胺的热膨胀系数不同,若其强度不足重布线层可能在温度变化时开裂。

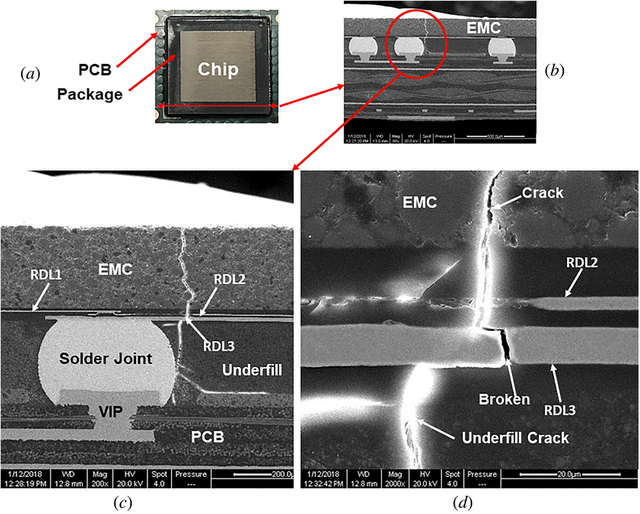

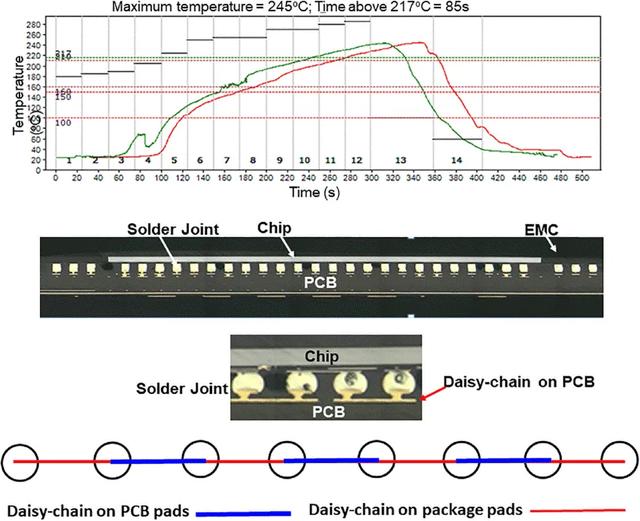

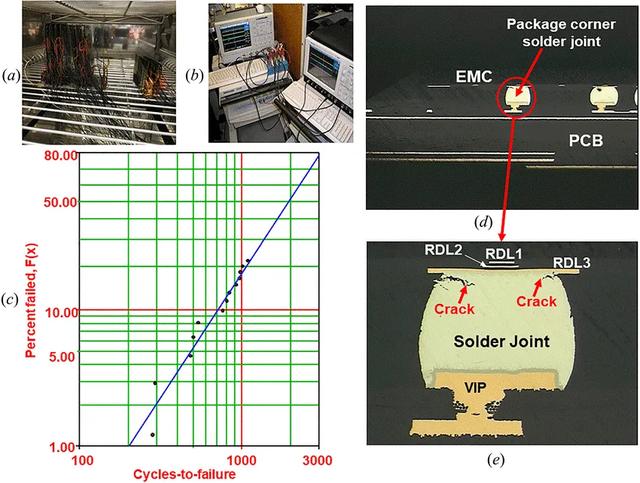

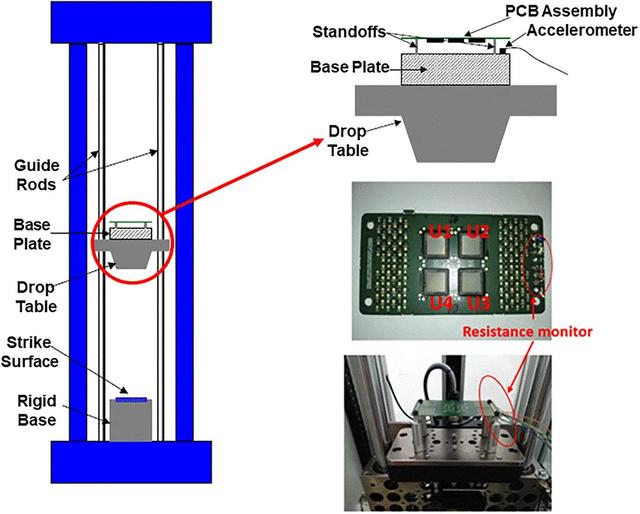

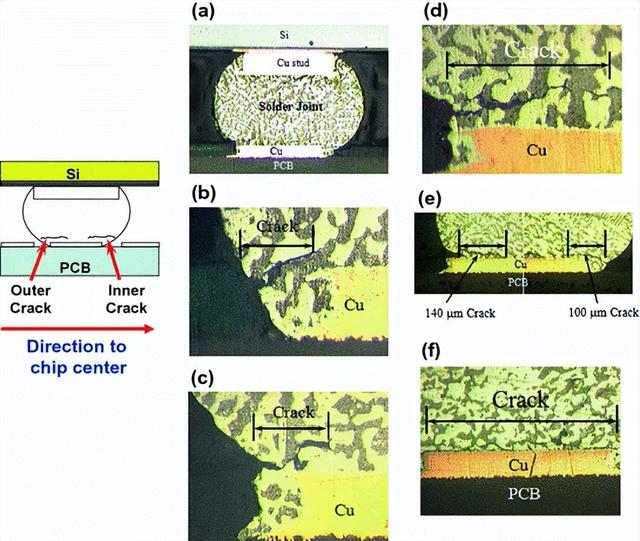

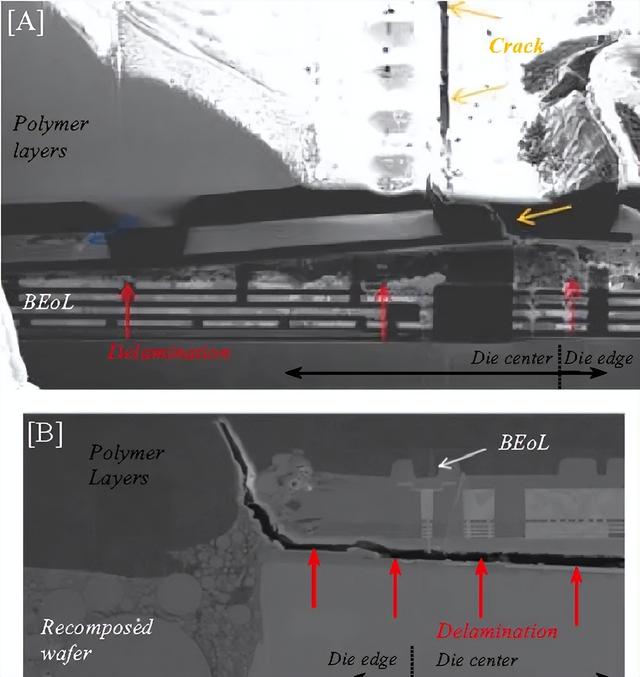

FOWLP应用中常见的失效模式包括重布线层分层和焊球开裂。菊花链测试链路可实时监测和定位FOWLP失效,有助于后续失效封装结构的分析。温度循环试验和冲击试验可有效暴露潜在的失效问题。

在发现失效后,可以利用超声波扫描电子显微镜(SAM)、扫描电子显微镜(SEM)、能量色散X射线光谱仪(EDX)、X射线能谱仪(EDS)等工具和方法对失效点进行定位和分析。超声波扫描电子显微镜和能量色散X射线光谱仪可准确定位失效位置,扫描电子显微镜可提供清晰图像,帮助理解失效原因。能谱分析可对失效点附近材料的成分进行分析,帮助追溯失效原因,如原材料纯度不足、清洗不彻底或生产环境不干净等。

温度循环试验和冲击试验可暴露布线层分层和焊球开裂风险。在温度循环测试中,重布线层的金属层和聚酰亚胺层会因不同的热膨胀系数而产生应力,可能导致开裂。冲击和温度循环也会导致焊球处的热应力和机械应力集中,不合理的产品设计或封装工艺可能导致焊球开裂。根据JEDEC发布的标准JESD22-A104,温度循环试验的范围为-40~125℃,循环次数为1000次,冲击测试的强度为1500g/ms。实际应用中,可靠性环境试验会根据产品生命周期阶段和应用场景进行调整,如航空航天产品可能会加强冲击测试,汽车电子产品可能会扩大温度循环范围或增加高温存储实验等。

03

主要工艺缺陷和失效模式

晶圆翘曲

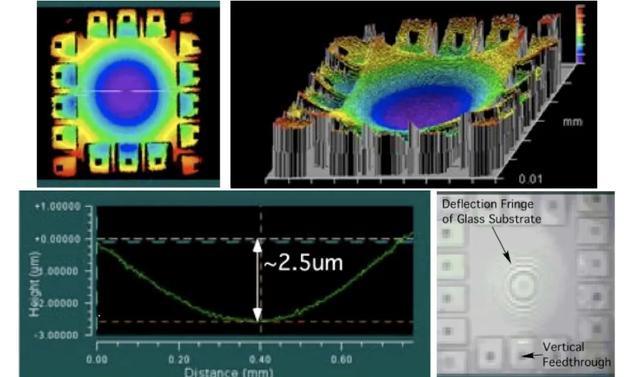

晶圆翘曲是由于加工过程中热机械应力的积累而导致晶圆在宏观上产生变形。这种变形会影响后续掩膜光刻的工艺精度,并限制再布线层密度的提升。晶圆翘曲会导致应力在中介层或焊点处集中,可能导致焊球开裂脱落和中介层分层等问题。晶圆尺寸越大,所受的热机械应力越强,翘曲现象也越严重。随着大尺寸芯片在晶圆级封装中的应用增多,晶圆翘曲问题已成为制约FOWLP发展的重要挑战。

由于晶圆表面容易划伤,行业常采用光学方法来测量其翘曲情况。这些方法主要分为光学干涉测量和激光扫描测量两类。光学干涉测量包括影子云纹法、投影云纹法和泰曼-格林干涉法,通过光栅干涉图像来描述晶圆的曲率。激光扫描测量则是利用激光对晶圆进行全面扫描定位,最终通过计算机拟合出晶圆翘曲的情况。

晶圆翘曲主要被认为是环氧塑封料固化引发的体积收缩和与不同材料的热膨胀系数不匹配导致的。然而,随着研究的深入,尤其是通过分析传统理论模型和实际结果之间的偏差,近年来发现了更多影响晶圆翘曲的因素。例如,硅的各向异性和环氧塑封料的粘弹性松弛效应也对翘曲产生一定影响。

芯片偏移

芯片偏移指晶片偏离其应有的位置。这种现象可通过高倍显微镜观察到,可能是因晶圆重构精度不足或后续工艺环节产生的应力所致。引发芯片偏移的应力主要有两种类型。一种是环氧塑封料在固化成型过程中的流动所产生的流体诱导阻力。另一种是封装过程中的热膨胀/收缩、环氧塑封料的固化收缩以及晶圆翘曲所导致的热机械应力。晶片边缘处的晶粒偏移最为严重,分析表明热机械效应和流体诱导阻力造成的应力具有相似的作用机制,即越靠近边缘,应力越大。晶圆重构过程中,临时载体黏附力不足是导致芯片偏移问题的最直接原因。与晶圆翘曲相比,引发芯片偏移的应力类型较少,失效机制更为明确。

焊点开裂

随着FOWLP的I/O接口数量不断增加,尺寸和焊点密度在不断提升。随着焊点体积的减小,单个焊点所受应力也越来越大,因此焊点的可靠性问题日益显著。

重布线层分层

重布线层中最常用的有机材料包括聚酰亚胺(PI)、聚苯并恶唑(PBO)和苯并环丁烯(BCB),此外还有酚醛树脂等。尽管PI是目前重布线层中使用最广泛的材料,但其固化温度较高,一般超过300℃。即使是经过改良的低温固化PI,其固化温度也在200℃以上,因此需要对工艺进行优化设计。重布线层的分层现象通常发生在温度循环测试之后,由于不同材料层反复经历热胀冷缩,导致材料间界面的疲劳应力而出现裂纹。此外,在冲击测试中也可能观察到重布线层分层现象。尽管重布线层分层是扇出型封装中常见的失效模式,但由于其结构和材料的复杂性,以及个性化的特点,重布线层的仿真难度较高,需要针对不同封装结构进行单独分析。

04

工艺改进和可靠性优化设计

通过实验和仿真,可以快速对工艺进行迭代,优化工艺参数,提升产品的良率。依赖成熟的失效物理模型对封装结构进行优化是提高产品可靠性的有效途径。

晶圆在制造工艺中经历了曲率、形状和方向的剧烈变化,最大翘曲不是在工艺结束时发生,而是在回流环节发生。因此,对于高密度的工艺操作,应该连续监测并有效控制每个工艺步骤的翘曲,而不是仅进行末端监控。

液体流动和热机械效应是导致芯片偏移的两大因素。通过降低塑封工艺速度和模具固化温度,缩小晶粒间距和晶粒厚度,以及增加环氧塑封料的厚度,可以减少液体流动带来的阻力,从而减少芯片偏移。另一方面,通过缩小环氧塑封料厚度,使用低热膨胀系数的临时载体,增加晶粒的间距和厚度,可以减少热机械效应引起的芯片偏移。然而,这些措施之间存在冲突,因此需要权衡工艺参数。针对不同的封装结构,反复进行建模和试验,才能使芯片偏移最小化。

重布线层分层的一个主要原因是生产环境的洁净度不足或者前一工艺环节残留物清洗不彻底。为了解决这个问题,需要严格监控生产环境,及时使用能谱分析技术检测分层的封装器件,找出导致分层的有机化合物并追溯来源,并及时进行整改。此外,在重布线工艺中,选择热膨胀系数与金属层匹配度高、分界层粘性大的有机材料也是减少分层的关键。

05

结语

FOWLP已经广泛应用于消费级和工业级半导体制造,并初步在高可靠芯片领域取得成功,成为未来商业竞争的关键技术。学术界和工业界已建立了大量的FOWLP可靠性物理模型,对其失效机理有了清晰认识,进行了一系列工艺改进和可靠性设计优化。然而,封装结构复杂度的提升以及多种应力的耦合关系使得仅依靠失效机理研究已难以指导深化工艺和设计改进。通过机器学习和深度学习,建立工艺过程、设计参数与产品良率、可靠性参数之间的数学关系和模型,可能是指导工艺和设计改进、进一步提升产品可靠性的有效途径,也是未来发展的一个重要方向。